# © Д. В. Ефанов, 2025

# КОНЕЧНЫЕ АВТОМАТЫ С САМОКОНТРОЛЕМ НА ОСНОВЕ ВЗВЕШЕННЫХ КОДОВ С СУММИРОВАНИЕМ И СВОЙСТВ САМОКВАЗИДВОЙСТВЕННЫХ БУЛЕВЫХ ФУНКЦИЙ

**ЕФАНОВ Дмитрий Викторович,** д-р техн. наук, профессор, действительный член Международной Академии транспорта, член Института инженеров электротехники и электроники, профессор<sup>1,2,3</sup>; e-mail: TrES-4b@yandex.ru

Описаны особенности организации контроля вычислений на выходах блоков конечных автоматов с использованием взвешенных кодов с суммированием и свойств самодвойственных и «близких» к ним самоквазидвойственных булевых функций. Предложена структура организации контроля вычислений по нескольким диагностическим признакам, основанная на использовании принципа логической коррекции сигналов от объекта диагностирования. Разработан алгоритм доопределения значений функций логической коррекции, используемый на этапе проектирования самопроверяемого дискретного устройства. Алгоритм подразумевает учет двух диагностических свойств: 1) каждый булев вектор на выходе блока коррекции сигналов в схеме встроенного контроля должен принадлежать множеству кодовых слов взвешенного кода с суммированием; 2) каждая функция, описывающая разряды булевых векторов, формируемых на выходах блока коррекции сигналов, должна быть самоквазидвойственной. Предложенный алгоритм позволяет синтезировать колоссальное количество вариаций схем встроенного контроля с различными показателями эффективности. Их использование на практике дает возможность выбора наилучшего способа организации схемы встроенного контроля по тому или иному критерию. Найдены некоторые оценки количества способов построения схем встроенного контроля для заданного числа входов и выходов объекта диагностирования. Предложенный метод универсален и может быть использован совместно с произвольными равномерными блоковыми кодами. Это, однако, потребует учета свойств кодов для обеспечения формирования проверяющих тестов на элементы схемы встроенного контроля в процессе эксплуатации самопроверяемого устройства. Полученные в исследовании результаты могут быть использованы при синтезе дискретных устройств с обнаружением неисправностей.

**Ключевые слова:** самопроверяемое дискретное устройство; самопроверяемый конечный автомат; схема встроенного контроля; взвешенный код с суммированием; самодвойственная булева функция; самоквазидвойственная булева функция; логическая коррекция сигналов в самоквазидвойственные; контроль вычислений по двум диагностическим признакам.

DOI: 10.20295/2412-9186-2025-11-01-75-102

## ▼ Введение

Системы ответственного назначения не обходятся без использования дискретных блоков и узлов, а многие технологические операции реализуются за счет выполнения ряда логических условий или их проверок. Эффективность технологического процесса и его безопасность определяются, в конечном итоге, надежностью и безопасностью самой системы автоматического

управления. Неисправности в блоках и узлах приводят к ошибкам в вычисляемых функциях и, как следствие, к нарушениям в реализации заложенных в управляющие системы алгоритмов. При построении дискретных устройств учитываются особенности элементной базы и условия эксплуатации конечного изделия в целях обеспечения своевременного обнаружения развивающихся или возникающих дефектов,

<sup>&</sup>lt;sup>1</sup>Санкт-Петербургский политехнический университет Петра Великого, Высшая школа транспорта, Институт машиностроения, материалов и транспорта, Санкт-Петербург

<sup>&</sup>lt;sup>2</sup>Российский университет транспорта, кафедра «Автоматика, телемеханика и связь на железнодорожном транспорте», Москва

<sup>&</sup>lt;sup>3</sup>Ташкентский государственный транспортный университет, кафедра «Автоматика и телемеханика», Ташкент

сигнализации техническому персоналу о возникновении событий отказов и парировании неверных результатов вычислений. В этой связи широко применяются методы синтеза дискретных устройств с контролепригодными, самопроверяемыми и отказоустойчивыми структурами [1—6], а также методы тестового и рабочего диагностирования [7, 8].

Свойство самопроверяемости дискретного устройства позволяет контролировать его работоспособность в процессе выполнения им своих функций и при наличии отказов и ошибок в вычислениях вырабатывать специальный контрольный сигнал. В этих целях требуется на этапе синтеза дискретного устройства заложить в его структуру некоторые особые свойства, несущие диагностические признаки, по которым и обнаруживаются неисправности. Часто при разработке дискретных устройств в качестве таких диагностических признаков выступают принадлежность вычисляемых на рабочих или контрольных выходах при подаче на входы определенных наборов значений аргументов булевых векторов заранее выбранным равномерным блоковым кодам [9, 10] либо же принадлежность каждой вычисляемой функции заранее выбранному особому классу булевых функций [11]. Исходя из этих диагностических признаков в структуру разрабатываемого устройства по определенным правилам вносится избыточность (причем эта избыточность может относиться и к структурному, и к информационному, и к временному резервированию как на уровне аппаратных, так и на уровне программных средств). Именно это позволяет контролировать корректность вычислений в процессе функционирования дискретного устройства и, тем самым, косвенно фиксировать наличие неисправностей в его внутренней структуре.

Несмотря на то, что теория синтеза самопроверяемых дискретных устройств развивается уже более полувека, в ней остаются незатронутые аспекты и даже целые области «спрятанных» знаний. В настоящей статье читателю предлагается к изучению метод синтеза схем встроенного контроля (СВК) для комбинационных составляющих дискретных устройств, позволяющий применять любые равномерные двоичные блоковые коды при организации контроля

вычислений сразу же по двум диагностическим признакам — контролю формируемых на выходах устройств булевых векторов множеству кодовых слов заранее выбранного равномерного блокового кода и контролю каждой функции, описывающей разряды кодовых слов классу «близких» к самодвойственным — самоквазидвойственным — функций. Метод основан на использовании хорошо известного принципа логической коррекции сигналов (ЛКС) [12, 13] и позволяет строить колоссальное количество реализаций СВК с различными показателями эффективности, среди которых можно выбрать наилучшие по тому или иному критерию. Кроме того, предложенный автором метод не требует существенного усложнения контрольного оборудования за счет использования естественных свойств булевых функций, описывающих поведение устройств на линиях СВК.

# 1. Самодвойственные и самоквазидвойственные булевы функции и дискретные устройства

Работа дискретных устройств описывается с использованием аппарата булевой алгебры. Среди всего многообразия булевых функций в дальнейшем изложении нам потребуются самодвойственные булевы функции [14] и «близкие» к ним самоквазидвойственные булевы функции [15].

Функция  $f(x_1, x_2, ..., x_t)$  называется самодвойственной, если

$$f(x_1, x_2, ..., x_t) = \overline{f(\overline{x_1}, \overline{x_2}, ..., \overline{x_t})}.$$

(1)

Функция  $f(x_1, x_2, ..., x_t)$  называется самоквазидвойственной, если

$$f(x_1, x_2, ..., x_t) = f(\overline{x_1}, \overline{x_2}, ..., \overline{x_t}).$$

(2)

Самодвойственные булевы функции принимают противоположные значения на парах наборов значений аргументов вида  $\langle x_t \ x_{t-1} \dots x_2 \ x_1 \rangle$ ,  $\langle \overline{x_t} \ \overline{x_{t-1}} \dots \overline{x_2} \ \overline{x_1} \rangle$ . Данные наборы ортогональны

<sup>&</sup>lt;sup>1</sup>В работах автора книги [15] и в некоторых более ранних работах автора настоящей статьи для обозначения самоквазидвойственных булевых функций использовался не совсем удачный термин «самоантидвойственный».

по всем аргументам. Самоквазидвойственные функции в чем-то схожи с самодвойственными, но принимают одинаковые значения на наборах, ортогональных по всем аргументам. Будем далее говорить о таких наборах как об инверсных наборах значений аргументов. Фактически будем выделять пары инверсных наборов значений аргументов. Для их обозначения используем десятичные числа, соответствующие двоичным числам, записываемым в качестве наборов значений аргументов. Тогда можно выделить  $2^{t-1}$  пар наборов вида:  $(j, 2^t - 1 - j), j \in \{0, 1, ..., 2^{t-1} - 1\}$ .

Используя свойства самодвойственных и самоквазидвойственных булевых функций, можно организовывать контроль вычислений на выходах дискретных устройств. Для этого необходимо фиксировать свойства рассматриваемых классов булевых функций, а именно — для самодвойственных функций фиксировать противоположные значения на каждой паре наборов значений аргументов  $(j, 2^t - 1 - j), j \in \{0, 1, ..., 2^{t-1} - 1\}$ , а для самоквазидвойственных — равенство значений функций при подстановке таких пар наборов значений аргументов.

На такую возможность относительно самодвойственных функций специалисты в области технической диагностики дискретных систем обратили внимание во второй половине прошлого столетия. В [16] предложены методы реализации булевых функций в виде схем, обладающих структурными свойствами для обнаружения любых одиночных константных неисправностей на линиях. Показано, что стандартная двухуровневая реализация схем в виде сетей И/ИЛИ или ИЛИ/И позволяет достигать этого свойства. Описаны и другие более общие структуры, наделенные этим свойством. Введены необходимые и достаточные условия, позволяющие обнаруживать неисправности при подаче на входы пар инверсных наборов значений аргументов.

Идеи работы [16] далее развивались в ряде публикаций, среди которых выделим статью [17]. В ней предложено синтезировать конечные автоматы, наделенные свойством самодвойственности булевых функций, реализуемых на выходах логических и выходных

преобразователей. Доказаны некоторые важные положения относительно вопроса синтеза самодвойственного конечного автомата (как полностью, так и частично определенного). Приведены примеры простейших конечных автоматов — триггеров.

Далее теория синтеза самодвойственных дискретных устройств развивалась в ряде работ научной школы профессоров Сапожниковых, где ими получены некоторые интересные результаты в области построения СВК с контролем вычислений по признаку самодвойственности булевых функций [18-21] и разработаны некоторые реализации самодвойственных триггеров [22, 23]. В части синтеза СВК данные работы фактически содержат методы организации контроля вычислений с предварительным сжатием сигналов от объекта диагностирования с использованием специальных преобразователей — кодеров равномерных блоковых кодов (причем ими рассматривались только приложения некоторых повсеместно используемых кодов - кодов с повторением, паритета, классических кодов Бергера и Хэмминга). Таким образом, т сигналов от объекта диагностирования сжимается в k сигналов на выходе кодера выбранного кода, которые затем с использованием двухвходовых сумматоров по модулю два (элементов ХОР) трансформируются в самодвойственные сигналы и контролируются в СВК (к слову, здесь как раз используется принцип ЛКС, упомянутый выше). Кроме того, профессорами Сапожниковыми был разработан единственный широко известный на сегодняшний день алгоритм синтеза защищенных от неисправностей структур с контролем вычислений по признаку самодвойственности вычисляемых функций, гарантирующий обнаружение любых одиночных неисправностей в них [24].

Следующий виток в развитии методов синтеза СВК с контролем вычислений при подаче на входы инверсных наборов значений аргументов связан с использованием не схем сжатия сигналов от объекта диагностирования, а полноценно всех свойств равномерных блоковых кодов совместно со свойствами самодвойственных булевых функций. В [25—28] предложены методы синтеза СВК

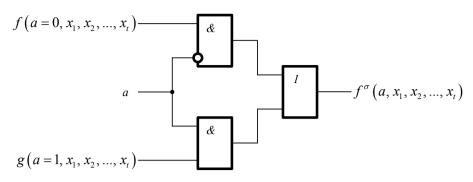

Рис. 1. Схема реализации самодвойственной и самоквазидвойственной функций

для устройств, выходы которых описываются самодвойственными булевыми функциями, подразумевающие использование для контроля вычислений и свойств равномерных блоковых кодов, и свойств самодвойственности формируемых в СВК функций. Ясно, что не все дискретные устройства обладают такими особенностями, но хорошо известно, например, из [29], что любую булеву функцию можно преобразовать в самодвойственную с использованием всего одной дополнительной переменной. Такое преобразование основано на разложении К. Э. Шеннона по одной переменной [30]:

$$f(x_1, ..., x_j, ..., x_t) =$$

$$= \overline{x_j} f(x_1, ..., 0, ..., x_t) \vee x_j f(x_1, ..., 1, ..., x_t),$$

$$j \in \{1, 2, ..., t\}.$$

(3)

Аналогично получаются и самоквазидвойственные реализации, на использование которых обратили внимание довольно давно (отнесем читателя к уже упомянутой монографии [15]), а вот на использование для контроля вычислений в дискретных устройствах — относительно недавно [31].

В соответствии с (3) можно получить самодвойственную или самоквазидвойственную булеву функцию так:

$$f^{\sigma}(a=0, x_1, x_2, ..., x_t) = -\overline{a}f(a=0, x_1, x_2, ..., x_t) \vee ag(a=1, x_1, x_2, ..., x_t),$$

(4)

где  $f\left(a=0,x_1,x_2,...,x_t\right)$  — исходная функция, не зависящая от переменной a;  $g\left(a=1,x_1,x_2,...,x_t\right)=f\left(\overline{x_1},\overline{x_2},...,\overline{x_t}\right)$ , если речь идет о самодвойственной реализации, и  $g\left(a=1,x_1,x_2,...,x_t\right)=f\left(\overline{x_1},\overline{x_2},...,\overline{x_t}\right)$ , если речь идет о самоквазидвойственной реализации

Структурно схема самодвойственного или самоквазидвойственного устройства будет реализовываться с применением оконечного каскада, изображенного на рис. 1. На первый вход верхнего элемента логического умножения (AND) данного каскада будет подключаться схема реализации функции  $f\left(a=0,x_1,x_2,...,x_t\right)$ , а на второй вход нижнего элемента AND данного каскада — схема реализации функции  $g\left(a=1,x_1,x_2,...,x_t\right)$ .

Таким образом, методы получения самодвойственных и самоквазидвойственных структур хорошо проработаны, а примеры их использования для преобразования произвольных структур в самодвойственные можно найти в [29].

Перейдем к особенностям реализации самодвойственных и самоквазидвойственных конечных автоматов и СВК для их комбинационных составляющих.

# 2. Самодвойственные и самоквазидвойственные автоматы с контролем вычислений

Конечный автомат представляет собой абстрактную модель дискретного устройства. Неисправности в его блоках и структурных единицах приводят к нарушениям алгоритма функционирования, и в системах

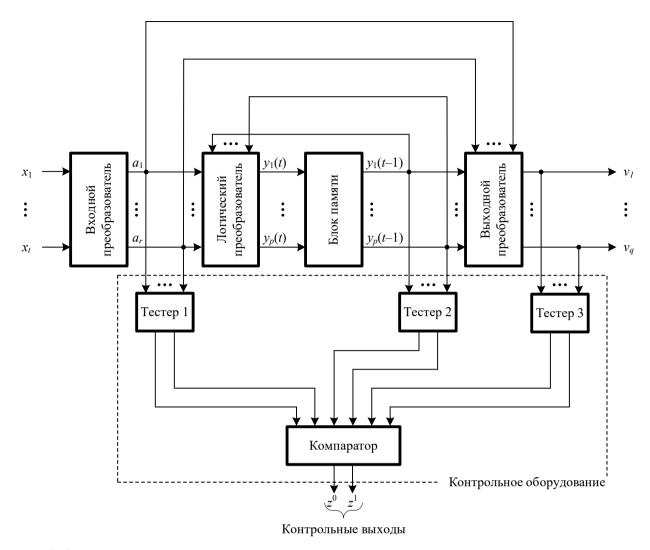

Рис. 2. Структура конечного автомата с контролем вычислений при кодировании входов, состояний и выходов

ответственного назначения они должны своевременно обнаруживаться, а неверно вычисленные результаты — блокироваться. Проблема обнаружения неисправностей в конечных автоматах хорошо известна и подробно исследована. Например, в [32] обсуждаются вопросы синтеза асинхронных конечных автоматов, свободных от критических состязаний, а также особенности синтеза автоматов, устойчивых к повреждениям внутренних компонентов, приводятся методы, позволяющие добиться свойства устойчивости автомата, основанные на разделении переходов и на временной коррекции блоков. В [33] приводятся методы синтеза конечных автоматов с обнаружением неисправностей, подразумевающие различные подходы — контроль вычислений на выходах входного, логического и выходного преобразователей. Все эти подходы основаны на внесении избыточности в конечный автомат с последующим контролем вычислений на выходах его блоков с помощью тестеров. На рис. 2 приводится структура конечного автомата с контролем вычислений на выходах входного, логического и выходного преобразователей. Эта структура позволяет синтезировать полностью самопроверяемые конечные автоматы.

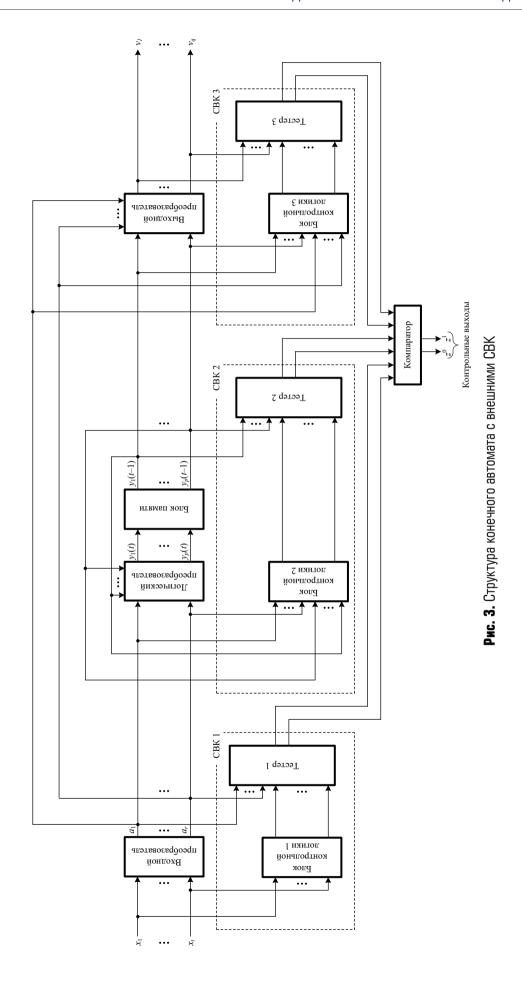

При синтезе конечного автомата по структуре рис. 2 в контролируемые блоки вносится избыточность. Другим способом синтеза полностью самопроверяемого конечного автомата является организации контроля вычислений с помощью внешних СВК. В этом случае в саму структуру конечного автомата избыточность не вносится, а требующиеся для обнаружения неисправностей элементы оказываются в выделенных СВК (рис. 3). Такой подход к организации самопроверяемого конечного

автомата позволяет наделять изначально спроектированное несамопроверяемое устройство данным свойством.

Хорошо известны и широко используются методы синтеза самопроверяемых конечных автоматов, основанные на использовании для обнаружения неисправностей и ошибок в вычислениях равномерных блоковых кодов с малой избыточностью. Наиболее часто в литературе можно встретить упоминание равновесных кодов, кодов с суммированием, кодов Хэмминга и их модификаций, используемых для решения задач синтеза конечных автоматов с обнаружением неисправностей и ошибок в вычислениях. Однако известны и другие способы построения самопроверяемых конечных автоматов. Одним из таковых является контроль вычислений по признаку самодвойственности и / или самоквазидвойственности вычисляемых на выходах комбинационных составляющих конечного автомата функций [31]. Такой способ построения конечного автомата требует временной избыточности для реализации, поскольку подразумевает работу в импульсном режиме при представлении сигналов логического 0 и логической 1 в виде последовательностей прямоугольных импуль- $\cos - 0101...01$  и 1010...10 соответственно.

Для построения самодвойственного и / или самоквазидвойственного конечного автомата достаточно реализовать конечный автомат в «обычном» виде, а затем комбинационные составляющие преобразовать в самодвойственные или же в самоквазидвойственные структуры. Элементы памяти при этом можно оставить стандартными, так как работать они будут в соответствии с принципами, заложенными в логический преобразователь на этапе его синтеза.

Известны следующие фундаментальные положения относительно самодвойственных конечных автоматов [17].

Утверждение 1. Полностью определенный конечный автомат будет самодвойственным конечным автоматом, если будет самодвойственной его комбинационная составляющая.

Утверждение 2. Неполностью определенный конечный автомат будет самодвойственным конечным автоматом, если будет самодвойственной его комбинационная часть и будет выполнено

следующее условие для любой пары  $X \varphi \subset \Psi$ , где  $\Psi$  — область определения автомата, X — входная последовательность,  $\varphi = Y_1 Y_2 \cdot ... \cdot Y_k$  — состояние автомата  $(Y_i, i=\overline{1,k}, -$  внутренние переменные):  $\overline{X} \varphi \subset \Psi$ .

Кроме того, отмечено, что в самодвойственном конечном автомате, в отличие от комбинационной схемы, для получения инвертированной выходной последовательности необходимо выполнить два условия: подать инвертированную входную последовательность и проинвертировать перед этим исходное начальное состояние автомата.

Нетрудно показать справедливость аналогичных утверждений и относительно самоквазидвойственных конечных автоматов.

**Утверждение 3.** Полностью определенный конечный автомат будет самоквазидвойственным конечным автоматом, если его комбинационная составляющая будет самоквазидвойственной схемой.

**Утверждение 4.** Неполностью определенный конечный автомат будет самоквазидвойственным автоматом, если его комбинационная часть будет самоквазидвойственной схемой и будет выполнено следующее условие для любой пары  $X \varphi \subset \Psi$ , где  $\Psi$  — область определения автомата, X — входная последовательность,  $\varphi = Y_1 Y_2 \cdot ... \cdot Y_k$  — состояние автомата  $(Y_i, i=\overline{1,k}, -$  внутренние переменные):  $\overline{X} \varphi \subset \Psi$ .

Дальнейшие исследования в теории синтеза самодвойственных и самоквазидвойственных конечных автоматов показали, что использованные ранее принципы контроля вычислений на выходах блоков конечных автоматов на основе равномерных блоковых кодов можно сочетать с контролем вычислений по признаку принадлежности булевых функций к особым и «близким» к ним классам булевых функций. Такое использование не требует существенного усложнения структуры конечного автомата (структуры наиболее часто оказываются менее сложными, чем структуры, подразумевающие дублирование автоматов). При этом значительно повышаются показатели контролепригодности в части наблюдаемости ошибок на контрольных выходах СВК. Улучшение показателей наблюдаемости ошибок достигает для различных видов неисправностей при различных конфигурациях элементов и связей между

ними в структуре конечного автомата 25—40 % по сравнению с контролем вычислений только по одному диагностическому признаку.

Рассмотрим далее, как организуются типовые СВК для контроля вычислений в таких конечных автоматах. При этом в качестве равномерных блоковых кодов будем использовать обширный класс взвешенных кодов с суммированием, обладающий определенными особенностями для их использования при синтезе самопроверяемых дискретных устройств.

# 3. Взвешенные коды с суммированием

Опишем здесь принципы построения взвешенных кодов с суммированием и поясним, почему же все-таки именно этот класс кодов так интересен при синтезе полностью самопроверяемых конечных автоматов.

Одни из первых взвешенных кодов с суммированием описаны в классической работе Дж. М. Бергера в 1961 г. [34]. Для обеспечения обнаружения любых двукратных искажений при сохранении свойства фиксации и однонаправленных (монотонных) искажений в кодовых словах было предложено не просто подсчитывать количество нулевых разрядов в информационных векторах при построении кода, а оперировать весовыми коэффициентами, заранее приписанными разрядам информационного вектора. Для этого использовалась специальная последовательность натуральных чисел — натуральный ряд за исключением степеней двойки (последовательность А057716 в энциклопедии Н. Дж. А. Слоана [35]). В дальнейших исследованиях того же специалиста для обнаружения пакетов ошибок заданной длины применялись те же принципы построения кода, но для соответствующих разрядов выбиралась последовательность степеней двойки (А000079) [36]. В последующем различные способы взвешивания при построении кодов с суммированием с различными свойствами изучались в [37-41].

Выбор больших значений весовых коэффициентов и их суммирование приводят к построению кодов с высокой избыточностью, что при использовании в процессе синтеза конечных автоматов отражается на показателях сложности их реализации. Для снижения избыточности кода используется модулярная

арифметика: суммарный вес информационного вектора подсчитывается в кольце вычетов по заранее установленному модулю

$$M \in \{2, 3, ..., W_{\text{max}} + 1\}, W_{\text{max}} = \sum_{i=1}^{m} w_i,$$

где  $w_i \in \mathbb{N}$  — значение весового коэффициента i-го разряда информационного вектора с общим числом разрядов (длиной информационного вектора), равным m.

Обозначим взвешенные коды как WS(m, k, M)-коды, где  $k = \lceil \log_2 M \rceil$  — количество проверочных символов в контрольных векторах (длина контрольного вектора).

Использование модуля M позволяет ограничивать длину контрольного вектора и, тем самым, не приводить к существенному усложнению компонентов конечных автоматов [42]. Наибольший интерес при рассмотрении вопросов синтеза конечных автоматов представляют WS(m, k, M)-коды с малым числом  $k \le 6$ . Соответственно, при построении таких взвешенных кодов с суммированием требуется использовать модуль  $M \le 64$  [41].

Особыми свойствами обладают WS(m, k, M)-коды, при построении которых выбирается модуль из множества

$$M \in \left\{ 2^{1}, 2^{2}, ..., 2^{\lceil \log_{2}(W_{\max} + 1) \rceil - 1}, 2^{\lceil \log_{2}(W_{\max} + 1) \rceil} \right\},$$

$$W_{\max} = \sum_{i=1}^{m} w_{i},$$

У таких кодов при определенных значениях  $m \ge m_{\min} (m_{\min} -$  некоторое граничное значение числа информационных разрядов для каждого значения M, при котором формируются все сочетания значений весовых коэффициентов) при рассмотрении полного множества информационных векторов (его мощность равна  $2^{m}$ ) в качестве контрольных векторов формируются все возможные двоичные векторы с k разрядами (мощность множества контрольных векторов равна  $2^k$ ). Эта особенность данного подкласса WS(m, k, M)-кодов учитывается при синтезе полностью самопроверяемой СВК на их основе: дело в том, что тестеры разделимых кодов наиболее часто синтезируется по двухкаскадной структуре, включающей в себя кодер и компаратор, для полной проверки которого и

потребуется формирование полного множества контрольных векторов с k разрядами [43, 44].

Еще одной особенностью взвешенных кодов с суммированием является то, что за счет взвешивания разрядов различными натуральными числами и подсчета суммарного веса в кольце вычетов по заданному модулю можно добиваться различных свойств обнаружения ошибок при фиксированном числе проверочных символов. Например, для широко используемых равновесных кодов или классических кодов с суммированием это невозможно. Для WS(m, k, M)-кодов при определенном взвешивании разрядов и выборе модуля из множества

$$M \in \left\{ 2^{1}, 2^{2}, ..., 2^{\lceil \log_{2}(W_{\max} + 1) \rceil - 1}, 2^{\lceil \log_{2}(W_{\max} + 1) \rceil} \right\},$$

$$W_{\max} = \sum_{i=1}^{m} w_{i},$$

можно достичь теоретического минимума общего количества необнаруживаемых ошибок в информационных векторах кодовых слов при заданных значениях m и k.

Можно сказать, что класс WS(m, k, M)-кодов, свойства которого до сих пор изучены не досконально (имеется лишь ограниченное количество работ в данном направлении, например, статья [41] и книга [45]), являются весьма перспективным классом равномерных разделимых кодов, использование которых будет эффективным по различным показателям при синтезе дискретных устройств с обнаружением неисправностей.

# 4. Структура организации контроля вычислений на выходах комбинационных составляющих конечных автоматов

Как известно [46, 47], комбинационные составляющие и элементы памяти тестируются с использованием разных принципов. Для комбинационных составляющих можно использовать самопроверяемые СВК, функционирующие параллельно с ними и проверяющие корректность вычислений на контролируемых выходах [2].

СВК на выходах комбинационных составляющих конечных автоматов по двум и более диагностическим признакам (принадлежность кодовых слов выбранному равномерному блоковому коду и принадлежность вычисляемых

функций самодвойственным и / или самоквазидвойственным) может быть синтезирована на основе традиционной структуры, подразумевающей дополнение информационных сигналов контрольными, либо на основе структуры, подразумевающей логическую коррекцию сигналов от объекта диагностирования.

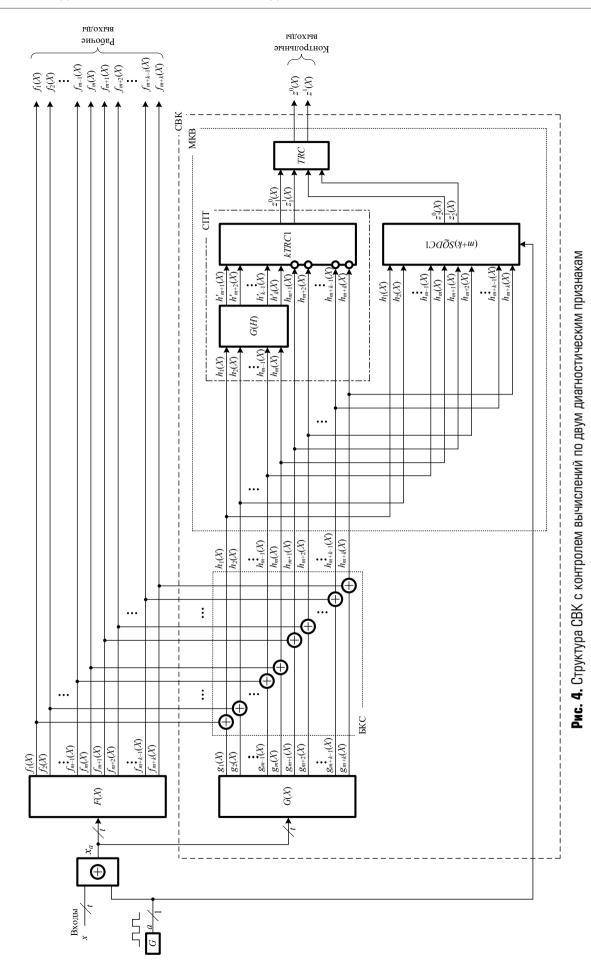

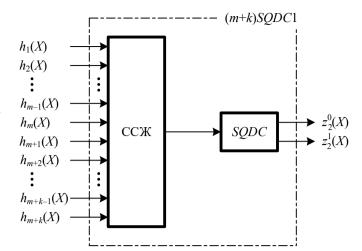

Синтез СВК на основе традиционной структуры с контролем вычислений по нескольким диагностическим признакам реализуется только для изначально самодвойственных или самоквазидвойственных комбинационных устройств с применением таких равномерных блоковых кодов, проверочные символы которых описываются самодвойственными и / или самоквазидвойственными булевыми функциями [27, 28]. При синтезе СВК с применением структуры на основе ЛКС подобных ограничений не требуется, так как самодвойственные и / или самоквазидвойственные сигналы получают в самой СВК путем преобразований функций, вычисляемых объектом диагностирования в определенные контролепригодные функции [27]. Данная структура изображена на рис. 4.

Объектом диагностирования является комбинационное устройство F(X), формирующее на каждом наборе значений аргументов  $\langle x_t | x_{t-1} ... x_2 | x_1 \rangle = \langle X \rangle$  конкретные булевы векторы  $< f_{m-k}(X) f_{m-k-1}(X) \dots f_2(X) f_1(X) >$ . Неисправности, возникающие в объекте диагностирования, приводят к возникновению ошибок на линиях его схемы, которые при подаче на входы определенных наборов значений аргументов транслируются на выходы в виде искажений истинных значений. Фиксируя данные искажения, можно косвенно судить об исправности или неисправности объекта диагностирования, соответственно, блокируя результаты вычислений им значений функций  $f_1(X)$ ,  $f_2(X)$ , ...,  $f_{m-k-1}(X)$ ,  $f_{m-k}(X)$ . Такую фиксацию обеспечивает использование специализированной СВК, включающей в себя несколько функциональных блоков.

Блок G(X) на тех же наборах значений аргументов, что и объект диагностирования, вычисляет значения функций логической коррекции сигналов  $g_1(X), g_2(X), ..., g_{m-k-1}(X), g_{m-k}(X)$ . Данные функции позволяют корректировать значения каждой функции  $f_1(X), f_2(X), ..., f_{m-k-1}(X), f_{m-k}(X)$  по правилу:

84

$$h_i(X) = f_i(X) \oplus g_i(X), i = \overline{1, m+k}. \tag{5}$$

Для реализации правила (5) используется блок коррекции сигналов (БКС), образованный каскадом из параллельно расположенных m+kдвухвходовых элементов ХОР. На первый вход каждого элемента ХОР подается значение функции  $f_i(X)$ , а на второй вход — значение функции коррекции  $g_i(X)$ . Тем самым, на выходе БКС получаются значения уже совершенно иных функций  $h_1(X),\ h_2(X),\ ...,\ h_{m+k-1}(X),\ h_{m+k}(X).$  На этапе проектирования эти функции наделяются особыми диагностическими свойствами. В рассматриваемом в настоящей статье приложении важно наделить эти функции двумя свойствами: первое свойство — это принадлежность каждого кодового слова  $< h_{m-k}(X) h_{m-k-1}(X) \dots h_2(X) h_1(X) >$ , формируемого на каждом наборе значений аргументов, выбранному WS(m, k, M)-коду; второе свойство - принадлежность каждой функции  $h_i(X)$  виду самоквазидвойственных булевых функций. Такими свойствами можно наделить функции  $h_1(X)$ ,  $h_2(X)$ , ...,  $h_{m+k-1}(X)$ ,  $h_{m+k}(X)$  на этапе проектирования СВК, используя специальные алгоритмы (один из таковых приведен ниже).

Для контроля вычислений по двум диагностическим признакам использован модуль контроля вычислений (МКВ). Он содержит две подсхемы контроля.

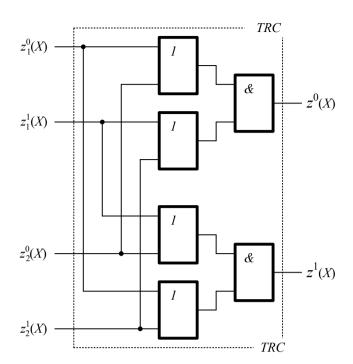

Первая подсхема контроля является самопроверяемым тестером (СПТ) WS(m, k, M)-кода и строится в виде двухкаскадной структуры «кодер + компаратор». Кодер G(H) по значениям входов  $h_1(X)$ ,  $h_2(X)$ , ...,  $h_{m-1}(X)$ ,  $h_m(X)$ формирует значения проверочных символов  $h'_{m+1}(X), \ h'_{m+2}(X), \ ..., \ h'_{m+k-1}(X), \ h'_{m+k}(X).$  Эти значения поступают на входы компаратора kTRC1, представляющего собой схему сжатия kпарафазных сигналов в один. На другие входы компаратора поступают значения проверочных символов  $h_{m+1}(X)$ ,  $h_{m+2}(X)$ , ...,  $h_{m+k-1}(X)$ ,  $h_{m+k}(X)$ , вычисленные в БКС. Компаратор производит сравнение значений функций с одинаковыми нижними индексами. Так как он оперирует парафазными сигналами, сигналы либо от блока G(H), либо от БКС предварительно инвертируются. В схеме рис. 4 инвертированы

**Puc. 5.** CTPYKTYPA (m+k)SQDC1

сигналы от БКС. Компаратор реализуется на основе (k-1) элементарного модуля сжатия парафазных сигналов TRC (two-rail checker) [48]. Данные модули самопроверяемы относительно модели одиночной константной неисправности и при наличии собственных неисправностей и ошибок в вычислениях формируют на выходах непарафазные сигналы. Выходы тестера  $z_1^0(X), z_1^1(X)$  являются контрольными выходами подсхемы контроля вычислений по WS(m, k, M)-коду.

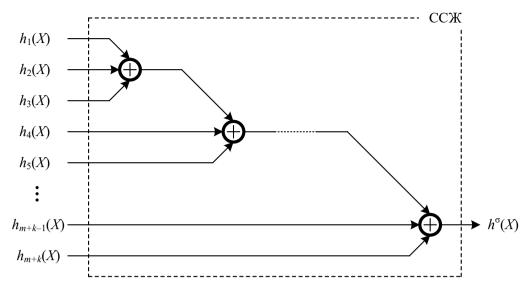

Вторая подсхема контроля вычислений (m+k)SQDC1 позволяет контролировать принадлежность каждой функции  $h_1(X)$ ,  $h_2(X)$ , ...,  $h_{m-1}(X)$ ,  $h_m(X)$  виду самоквазидвойственных функций. Наиболее простая реализация (m+k) SQDC1 представляет собой схему сжатия (m+k) самоквазидвойственных сигналов в один и элементарный тестер самоквазидвойственного сигнала (рис. 5).

Схема сжатия (ССЖ) самоквазидвойственных сигналов аналогична схеме сжатия самодвойственных сигналов [49]. Она синтезируется на основе трехвходовых элементов *XOR* по структуре, представленной на рис. 6. Если на входы одного элемента *XOR* подается самоквазидвойственный сигнал, то на его выходе также присутствует самоквазидвойственный сигнал. Для

реализации схемы сжатия требуется  $\left\lfloor \frac{m+k}{2} \right\rfloor$

трехвходовых элементов ХОЯ. Особенностью

Рис. 6. Схема сжатия самоквазидвойственных сигналов

Рис. 7. Тестер самоквазидвойственных сигналов

обустройства схемы сжатия самоквазидвойственных сигналов является то, что при нечетном значении (m+k) все сигналы  $h_1(X)$ ,  $h_2(X)$ , ...,  $h_{m+k-1}(X)$ ,  $h_{m+k}(X)$  подаются на входы схемы сжатия, а при четном значении (m+k) на один из входов одного из XOR требуется подача сигнала a от генератора G прямоугольных импульсов.

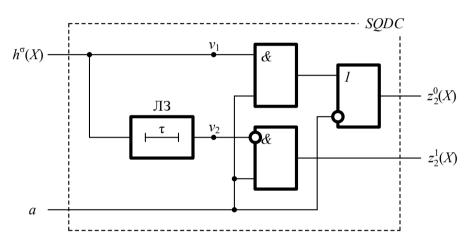

Использование схемы сжатия позволяет сократить до одного количество тестеров самоквазидвойственных сигналов SQDC (self quasidual checker). Структура простейшего SQDC изображена на рис. 7. Он работает аналогично тестеру самодвойственных сигналов [50]. На вход  $h^{\sigma}(X)$  подается последовательность сигналов 0 и 1. Фактически тестер распознает пары подаваемых сигналов. Последовательный сигнал  $h^{\sigma}(X)$  в SQDC преобразуется в параллельный

двухфазный сигнал, формируемый в точках  $v_1$  и  $v_2$ . Это преобразование осуществляется с использованием линии задержки (ЛЗ). Длительность т задержки равна одному такту последовательности а, формируемой на выходе генератора G. Так как сигнал  $h^{\sigma}(X)$  является самоквазидвойственным, то в любой момент времени в отсутствие неисправностей и ошибок в вычислениях  $v_1 = v_2$ . Поскольку сигнал v<sub>2</sub> инвертируется на первом входе второго элемента AND в схеме SQDC, в контрольном такте (при a = 1) на выходе тестера фиксируется парафазный сигнал  $z_2^0(X) \neq z_2^1(X)$ . При наличии ошибок в вычислениях, приводящих к искажению одного из сигналов в подаваемой паре  $v_1 \neq v_2$ , за счет наличия инверсии сигнала  $v_2$ на первом входе второго элемента AND в схеме

SQDC в контрольном такте (при a=1) устанавливаются одинаковые сигналы на выходах обоих элементов AND и, как следствие, формируется непарафазный сигнал  $z_2^0(X) = z_2^1(X)$  на выходах. Здесь следует отметить, что работа генератора и тестера самоквазидвойственных сигналов должна быть синхронизирована [50].

Для получения одного-единственного сигнала контроля  $< z^0(X)$   $z^1(X) >$  используется элементарный модуль TRC. На рис. 8 приведена одна из структур хорошо известных модулей сжатия парафазных сигналов [51]. Могут быть использованы и другие реализации модулей сжатия парафазных сигналов.

Таким образом, при незначительном усложнении контрольного оборудования в СВК за счет использования устройства (m+k)SQDC1 и одного дополнительного модуля TRC удается использовать сразу же два диагностических свойства.

Однако только этого недостаточно для работы устройства с СВК. Контроль вычислений по признаку самоквазидвойственности булевых функций требует временной избыточности и функционирования всей структуры в импульсном режиме при инвертировании данных [17].

Для реализации импульсного режима работы структуры, представленной на рис. 4, устанавливается генератор G. Он формирует прямоугольные импульсы а со скважностью 2. Они используются для получения из входных переменных  $x_1, x_2, ..., x_t$  последовательностей импульсов и для работы тестера самоквазидвойственных сигналов. Каждый сигнал с каждого входа преобразуется в последовательность импульсов: логический ноль преобразуется в последовательность 0101...01, а логическая единица — в последовательность 1010...10. Это делается за счет использования t двухвходовых элементов ХОР, на первые входы которых подаются сигналы  $x_1, x_2, ..., x_t$ , а на вторые — последовательность а. Таким образом, наборы значений аргументов начинают генерироваться на входах объекта диагностирования парами рабочая и контрольная комбинации. Причем, вторая является ортогональной по всем аргументам для первой. Особенности работы схем в таком режиме описаны в [29].

Рис. 8. Модуль сжатия парафазных сигналов

Структура, приведенная на рис. 4, и аналогичная ей ранее исследовались в некотором довольно малом количестве работ (единичные работы автора данной статьи). Например, фактически аналогичная представленной на рис. 4 структура применена в [25, 26] для контроля вычислений по признаку принадлежности кодовых слов равновесному коду «2 из 4» и по признаку самодвойственности каждой функции, описывающей разряды кодовых слов. В [52] данная структура применена при организации СВК с использованием кодов с суммированием весовых коэффициентов пар подряд следующих в информационном векторе разрядов вида  $(f_1(X), f_2(X)), (f_2(X), f_3(X)), ..., (f_{m-1}(X), f_m(X))$  (это так называемый код с суммированием взвешенных переходов [53, 54]). Он обладает тем свойством, что ортогональные по всем разрядам информационные векторы для него имеют одинаковые контрольные векторы, что говорит о самоквазидвойственности проверочных символов данных кодов. Такое свойство позволяет применять данный вид взвешенных кодов с суммированием для контроля вычислений по двум и более диагностическим признакам.

Приведем далее универсальный метод организации СВК по двум диагностическим признакам, позволяющий применить любой разделимый блоковый код в этих целях.

Используем, однако, только WS(m, k, M)-коды, поскольку они обладают важными свойствами, обеспечивающими простоту процедур полной проверки контрольного оборудования СВК в процессе эксплуатации готового устройства.

# 5. Метод организации схемы встроенного контроля по двум диагностическим признакам с использованием взвешенных кодов с суммированием

В качестве основы СВК, синтезируемой по структуре, изображенной на рис. 4, возьмем WS(m, k, M)-коды со значением

$$\begin{split} M \in & \left\{ 2^{1}, 2^{2}, ..., 2^{\left\lceil \log_{2}(W_{\max} + 1) \right\rceil - 1}, 2^{\left\lceil \log_{2}(W_{\max} + 1) \right\rceil} \right\}, \\ W_{\max} &= \sum_{i=1}^{m} w_{i}, \end{split}$$

Выбор значения модуля в виде степени двойки обусловлен тем, что при таком модуле для полного множества информационных векторов будет генерироваться и полное множество контрольных векторов с числом проверочных символов k. Для модулей, не являющихся степенями двойки, это свойство недостижимо. Как отмечалось выше, формирование хотя бы единожды каждого контрольного вектора с числом разрядов k требуется для полной проверки тестера разделимого кода.

В зависимости от значений M и m можно построить большое количество WS(m, k, M)-кодов с различными массивами весовых коэффициентов  $[w_m, w_{m-1}, ..., w_2, w_1]$ , приписываемых разрядам информационных векторов.

Опишем далее метод, позволяющий использовать структуру, приведенную на рис. 4, для контроля вычислений по WS(m, k, M)-кодам. Данный метод базируется на использовании следующего алгоритма.

Правила синтеза СВК по двум диагностическим признакам на основе WS(m, k, M)-кодов:

1. Формируется таблица описания сигналов на линиях СВК, куда заносятся все значения аргументов  $x_1, x_2, ..., x_l$ , значения функций  $f_1(X), f_2(X), ..., f_{m-k-1}(X), f_{m-k}(X)$ , которые полностью определены, выделяются графы

для неопределенных на данном этапе значений функций логической коррекции сигналов  $g_1(X), g_2(X), ..., g_{m-k-1}(X), g_{m-k}(X)$  и функций  $h_1(X), h_2(X), ..., h_{m-k-1}(X), h_{m-k}(X)$ , описывающих разряды кодовых слов WS(m, k, M)-кодов.

2. С учетом условия

$$2^{t-1} \ge 2^k \iff k \le t - 1 \tag{6}$$

определяются параметры m, k, M для кода с суммированием.

Выполнение этого условия необходимо по причине того, что потребуется сформировать полное множество контрольных векторов с k проверочными символами.

- 3. Выбирается последовательность весовых коэффициентов  $[w_m, w_{m-1}, ..., w_2, w_1]$ , приписываемых разрядам информационных векторов, и фиксируется конкретный WS(m, k, M)-код.

- 4. Формируется таблица распределения информационных векторов на группы, соответствующие контрольным векторам, для данного WS(m, k, M)-кода. В процессе доопределения значений функций  $h_1(X)$ ,  $h_2(X)$ , ...,  $h_{m-k-1}(X)$ ,  $h_{m-k}(X)$  необходимо использовать хотя бы один информационный вектор с каждым из имеющихся контрольных векторов.

- 5. Наборы значений аргументов, представляющие собой двоичные числа от <00...00> до <11...11>, соответствующие десятичным эквивалентам от 0 до  $2^t-1$ , разбиваются на пары  $(j, 2^t-1-j), j \in \{0, 1, ..., 2^{t-1}-1\}$ . В иной трактовке рассматривается первая половина таблицы описания с номерами строк от 0 до  $2^{t-1}-1$ .

- 6. На каждом наборе значений аргументов, соответствующих первому десятичному числу из пары  $(j, 2^t 1 j), j \in \{0, 1, ..., 2^{t-1} 1\}$ , осуществляется доопределение значений разрядов вектора  $< h_{m-k}(X)h_{m-k-1}(X)...h_2(X)h_1(X)>$  до произвольного кодового слова WS(m, k, M)-кода. В процессе доопределения должны быть использованы хотя бы единожды кодовые слова с различными контрольными векторами.

- 7. На каждом наборе значений аргументов, соответствующих второму десятичному числу из пары  $(j, 2^t 1 j), j \in \{0, 1, ..., 2^{t-1} 1\}$ , осуществляется доопределение значений разрядов вектора  $\langle h_{m-k}(X) \ h_{m-k-1}(X) \ ... \ h_2(X) \ h_1(X) \rangle$  до

использованного ранее при доопределении значений этого вектора на наборе значений аргументов, соответствующих первому десятичному числу в рассматриваемой паре, кодового слова WS(m, k, M)-кода. Именно в таком случае каждая функция  $h_1(X)$ ,  $h_2(X)$ , ...,  $h_{m-k-1}(X)$ ,  $h_{m-k}(X)$  окажется самоквазидвойственной.

8. Определяются значения функций логической коррекции сигналов:

$$g_i(X) = f_i(X) \oplus h_i(X), i = \overline{1, m+k}. \tag{7}$$

- 9. Проверяется формирование полных тестов для элементов *XOR* в БКС. Как известно [55], полный тест для элемента *XOR* в канонической его реализации содержит все четыре комбинации {00, 01, 10, 11}.

- 10. Если тесты для каждого XOR формируются, то переходят к следующему пункту алгоритма; в противном случае возвращаются на шаг 6 и выполняют иное доопределение векторов  $< h_{m-k}(X) \ h_{m-k-1}(X) \ ... \ h_2(X) \ h_1(X)>$ , либо меняют последовательность при построении WS(m,k,M)-кода, либо параметры кода.

- 11. Функции  $g_1(X), g_2(X), ..., g_{m-k-1}(X), g_{m-k}(X)$  оптимизируются по отдельности или совместно с использованием любого метода [56].

- 12. Устройство с СВК синтезируется в выбранном элементном базисе.

Ясно, что основной задачей синтеза будет являться получение описания работы блока G(X). Далее процедура синтеза реализуется понятным образом и не требует дополнительного пояснения.

Приведем пример использования разработанного автором настоящей статьи алгоритма при синтезе СВК по двум диагностическим признакам. Требуется получить функции, задающие логику работы блока G(X) в СВК, реализованной с использованием предложенного алгоритма и структуры, приведенной на рис. 4, для устройства, описываемого табл. 1.

Итак, объект диагностирования F(X) имеет t = 4 и n = 8 выходов.

На первом этапе таблица описания устройства F(X) расширяется. В нее добавляются столбцы  $g_1(X),\ g_2(X),\ ...,\ g_7(X),\ g_8(X)$  и  $h_1(X),\ h_2(X),\ ...,\ h_7(X),\ h_8(X)$ .

Далее определяются параметры WS(m, k, M)-кода.

Следуя за (6), установим ограничения на значение числа проверочных символов в кодовых словах взвешенного кода с суммированием:  $k \le 3$ . В нашем случае требуется использовать WS(m, k, M)-код со значениями модулей M = 2, 4 или 8. Хорошо известно, что помехозащищенный взвешенный код с суммированием с модулем M = 2 соответствует коду паритета, не обнаруживающему любые ошибки с четными кратностями [44]. Поэтому для организации СВК целесообразно рассматривать два семейства WS(m, k, M)-кодов — с M = 4 и M = 8. Вообще, здесь и далее код паритета из рассмотрения исключается, хотя и его можно было бы применить при синтезе СВК по предложенному методу с некоторыми ограничениями, связанными с особенностями выделения контролируемых групп выходов объекта диагностирования или же предварительными преобразованиями его структуры в контролепригодную по данному коду [2].

Ограничимся в данном примере рассмотрением использования только кода с наибольшим значением модуля — WS(5, 3, 8)-код. Здесь M=8 и k=3, а число информационных разрядов определено исходя из того, что  $n=m+k \Leftrightarrow m=n-k$ .

Существует большое количество способов построения WS(5, 3, 8)-кодов —  $(M-1)^m = 7^5 = 16~807~[45]$ . Все эти способы определяются числом вариантов взвешивания разрядов информационного вектора. Зафиксируем одну, абсолютно случайную, из последовательностей весовых коэффициентов  $[w_8, w_7, w_6, w_5, w_4] = [5, 6, 1, 2, 1]$  (здесь использованы нижние индексы для весовых коэффициентов, соответствующие нижним индексам функций, выделенных «под информационные разряды»).

Подчеркнем, что в рассматриваемом примере было использовано произвольное распределение весовых коэффициентов при построении WS(m, k, M)-кода. Но на практике конкретные сочетания значений для весовых коэффициентов определяют и характеристики обнаружения ошибок строящимися кодами, и в существенной мере влияют на процедуры обеспечения формирования проверяющих

Таблица 1. Описание работы устройства с СВК

| (X) <sup>L</sup> 6 | 0 | 0        | -        | - | 0 | 0        | -        | - | -        | -        | 0        | 0                                       | 0  | 0        | -  | -  |

|--------------------|---|----------|----------|---|---|----------|----------|---|----------|----------|----------|-----------------------------------------|----|----------|----|----|

| (χ) <sup>ζ</sup> δ | - | <b>—</b> | 0        | 0 | 0 | -        | 0        | 0 | <b>—</b> | <b>—</b> | 0        | <del>-</del>                            | -  | 0        | -  | 0  |

| (χ) <sup>ε</sup> δ | 0 | <b>—</b> | 0        | 0 | 0 | <b>-</b> | <b>-</b> | - | 0        | <b>—</b> | 0        | <b>—</b>                                | 0  | 0        | -  | 0  |

| (χ) <sup>†</sup> δ | 0 | _        | _        | 0 | _ | _        | 0        | 1 | _        | -        | 0        | 0                                       | 0  | 0        | 1  | -  |

| (X) <sup>S</sup> 6 | 0 | 0        | 0        | 0 | 0 | <b>-</b> | <b>-</b> | 0 | 0        | 0        | <b>—</b> | <b>—</b>                                | -  | 0        | -  | 0  |

| (X) <sup>9</sup> 6 | 1 | 0        | 0        | _ | 0 | -        | 0        | 0 | _        | 0        | 0        | _                                       | 0  | 0        | 0  | -  |

| (X) <sup>L</sup> 6 | 1 | _        | 0        | 0 | _ | _        | -        | 0 | 0        | -        | 0        | _                                       | 0  | 0        | -  | 0  |

| (X) <sup>8</sup> 6 | 0 | <b>—</b> | <b>—</b> | 0 | 0 | <b>—</b> | <b>—</b> | 0 | 0        | 0        | <b>—</b> | 0                                       | _  | <b>—</b> | 0  | 0  |

| (X) <sup>L</sup> Y | 0 | _        | 0        | _ | 0 | _        | 0        | - | _        | 0        | _        | 0                                       | -  | 0        | -  | 0  |

| (X) <sup>Z</sup> Y | 0 | 0        | _        | _ | 0 | 0        | _        | - | _        | -        | 0        | 0                                       | -  | _        | 0  | 0  |

| (χ) <sup>ε</sup> 4 | 0 | 0        | 0        | 0 | - | -        | -        | - | -        | -        | -        | -                                       | 0  | 0        | 0  | 0  |

| (X) <sup>†</sup> Ч | 0 | -        | 0        | - | - | 0        | 0        | - | -        | 0        | 0        | -                                       | -  | 0        | -  | 0  |

| (x) <sup>≤</sup> 4 | 0 | 0        | -        | - | - | 0        | 0        | 0 | 0        | 0        | 0        | <b>—</b>                                | -  | -        | 0  | 0  |

| (X) <sup>9</sup> 4 | 0 | 0        | 0        | 0 | - | 0        | 0        | 0 | 0        | 0        | 0        | -                                       | 0  | 0        | 0  | 0  |

| (X) <sup>L</sup> Y | 0 | 0        | 0        | 0 | 0 | 0        | -        | - | -        | -        | 0        | 0                                       | 0  | 0        | 0  | 0  |

| (X) <sup>8</sup> 4 | 0 | 0        | 0        | 0 | 0 | -        | 0        | 0 | 0        | 0        | -        | 0                                       | 0  | 0        | 0  | 0  |

| (X) <sup>1</sup> J | 0 | -        | -        | 0 | 0 | -        | -        | 0 | 0        | -        | -        | 0                                       | -  | 0        | 0  | -  |

| (X) <sub>z</sub> ì | 1 | -        | -        | - | 0 | -        | -        | - | 0        | 0        | 0        | -                                       | 0  | -        | -  | 0  |

| (X) <sub>E</sub> J | 0 | -        | 0        | 0 | - | 0        | 0        | 0 | -        | 0        | -        | 0                                       | 0  | 0        | -  | 0  |

| (X) <sub>p</sub> ì | 0 | 0        | -        | - | 0 | -        | 0        | 0 | 0        | -        | 0        | -                                       | -  | 0        | 0  | -  |

| (X) <sup>2</sup> J | 0 | 0        | -        | - | - | -        | -        | 0 | 0        | 0        | _        | 0                                       | 0  | -        | -  | 0  |

| (X) <sup>9</sup> J | 1 | 0        | 0        | - | - | -        | 0        | 0 | -        | 0        | 0        | 0                                       | 0  | 0        | 0  | -  |

| (X) <sup>∠</sup> ៛ | 1 | -        | 0        | 0 | - | -        | 0        | - | -        | 0        | 0        | <b>—</b>                                | 0  | 0        | -  | 0  |

| (X) <sub>8</sub> f | 0 | -        | -        | 0 | 0 | 0        | -        | 0 | 0        | 0        | 0        | 0                                       | -  | -        | 0  | 0  |

| ι <sub>χ</sub>     | 0 | -        | 0        | - | 0 | -        | 0        | - | 0        | -        | 0        | -                                       | 0  | -        | 0  | -  |

| τ <sub>χ</sub>     | 0 | 0        | -        | - | 0 | 0        | -        | - | 0        | 0        | <b>—</b> | <b>—</b>                                | 0  | 0        | -  | -  |

| ٤χ                 | 0 | 0        | 0        | 0 | - | -        | -        | - | 0        | 0        | 0        | 0                                       | -  | -        | -  | -  |

| <sup>ъ</sup> х     | 0 | 0        | 0        | 0 | 0 | 0        | 0        | 0 | -        | -        | <b>—</b> | <b>—</b>                                | -  | -        | -  | -  |

| ьqодьн qэмоH       | 0 | -        | 7        | ĸ | 4 | 2        | 9        | 7 | œ        | 6        | 10       | ======================================= | 12 | 13       | 14 | 15 |

Таблица 2. Распределение информационных векторов WS(5, 3, 8)-кода между контрольными векторами

|       |       |       | Контрольн   | Контрольные векторы    |       |       |       |

|-------|-------|-------|-------------|------------------------|-------|-------|-------|

| 000   | 001   | 010   | 011         | 100                    | 101   | 110   | 111   |

|       |       |       | Информацион | Информационные векторы |       |       |       |

| 00000 | 00001 | 00010 | 00011       | 00111                  | 10000 | 01000 | 01001 |

| 01010 | 00100 | 00101 | 00110       | 11001                  | 11010 | 10001 | 01100 |

| 01101 | 01011 | 01111 | 11000       | 11100                  | 11101 | 10100 | 10010 |

| 10011 | 01110 |       |             |                        |       | 11011 | 10101 |

| 10110 | 10111 |       |             |                        |       | 11110 | 11111 |

комбинаций в процессе эксплуатации готового устройства. Например, за счет изменения значений весовых коэффициентов при построении WS(m, k, M)-кода при невозможности обеспечить самопроверяемость БКС можно осуществить подбор весовых коэффициентов, обеспечивающих решение этой задачи.

Для заполнения табл. 1 потребуется таблица распределения информационных векторов между контрольными векторами рассматриваемого *WS*(5, 3, 8)-кода (табл. 2). Каждому контрольному вектору данного кода соответствует либо три, либо пять информационных векторов. Следует отметить, что данный WS(5, 3, 8)-код не является кодом с обнаружением максимального количества ошибок в информационных векторах как раз из-за неравномерности распределения информационных векторов между контрольными векторами [44, 45]. Это не повлияет на процедуру синтеза СВК, но должно учитываться при покрытии кодом ошибок на выходах объекта диагностирования.

Далее, при доопределении значений разрядов вектора  $< h_{m-k}(X) \, h_{m-k-1}(X) \dots h_2(X) \, h_1(X) >$  на каждом наборе значений аргументов используем по одному кодовому слову с одним и тем же контрольным вектором. Возьмем, например, первые информационные векторы из табл. 2:  $<00000\,000>$ ,  $<00001\,001>$ ,  $<00010\,010>$ ,  $<00011\,011>$ ,  $<00111\,100>$ ,  $<10000\,101>$ ,  $<01000\,110>$  и  $<01001\,111>$ . Заполним последовательно первые восемь строк табл. 1 каждым выбранным кодовым словом. Аналогичное заполнение выполним симметрично относительно середины табл. 2.

Далее с использованием (7) получим значения функций логической коррекции сигналов. Они также уже занесены в табл. 1.

Проверка формирования полных тестов для элементов преобразования в БКС (построчная проверка столбцов  $f_i(X)$  и  $g_i(X)$ ) показала, что для всех элементов XOR, кроме  $XOR_8$  формируются полные тесты. Для  $XOR_8$  не формируется тестовая комбинация <10>. Поменяем используемое кодовое слово для доопределения значений вектора  $<hat holdsymbol{hg}(X)$   $h_7(X)$  ...  $h_2(X)$   $h_1(X)$ >. Для этого выделим в графе  $f_8(X)$  те строки, которые соответствуют необходимым тестовым комбинациям из множества  $\{00, 01, 10\}$ . Это строки с

номерами 0, 1, 5. Далее среди оставшихся строк найдем те, в которых имеется единица, так как не хватает именно комбинации <10>. Выберем такое кодовое слово для доопределения значений вектора  $< h_8(X) \ h_7(X) \ ... \ h_2(X) \ h_1(X)>$ , в котором для строки, соответствующей выбранному значению единицы в столбце  $f_8(X)$  будет зафиксировано противоположное значение. Возьмем строку номер 12. В ней кодовое слово  $< h_8(X) \ h_7(X) \ ... \ h_2(X) \ h_1(X)>$  доопределено до слова  $< 00011 \ 011>$ , принадлежащего WS(5, 3, 8)-коду. Обратимся к табл. 2. Выберем в ней кодовое слово, в котором  $f_8(X)$ =1 — кодовое слово  $< 11000 \ 011>$ . Заполним строки с номерами 12 и 3 кодовым словом  $< 11000 \ 011>$ .

Обновленный вариант доопределения значений векторов  $\langle h_8(X) \ h_7(X) \ ... \ h_2(X) \ h_1(X) \rangle$  и значений функций логической коррекции сигналов представлен в табл. 3. Строки с измененными значениями сигналов выделены.

Простая проверка показывает, что скорректированная таблица описания работы устройства с СВК отвечает требованиям полной проверки элементов преобразования в БКС.

Таким образом, функции, реализуемые на выходах блока G(X), заданы на каждом наборе значений аргументов в табл. 3. Из таблицы легко получить логические выражения, описывающие данные функции, используя любой из известных методов [56].

Чем больше разница (t-k), тем проще обеспечивать формирование полных тестов для элементов преобразования. Однако здесь следует обратить внимание на то, что хотя бы на двух наборах значений аргументов должны формироваться значения 0 (1) для функций, описывающих выходы объекта диагностирования. В противном случае не удастся ни при каких способах обеспечить полную самопроверяемость БКС [57]. Это справедливо и для традиционных методов синтеза СВК.

Трудоемкость разработанного алгоритма определяется числом t входов объекта диагностирования. Она может быть асимптотически оценена величиной  $2^{O(t)}$ , т. е. задача доопределения значений  $< h_{m-k}(X) \ h_{m-k-1}(X) \ ... \ h_2(X) \ h_1(X) >$  на каждом наборе значений аргументов решается за экспоненциальное время с линейной экспонентой. Наиболее эффективно задача решается

|                                                        | (X) <sup>1</sup> 6    | 0          | 0            | - | - | 0           | 0            | -        | -        | <b>—</b>     | <del>-</del> | 0            | 0 | 0  | 0            | <b>—</b>     | -  |

|--------------------------------------------------------|-----------------------|------------|--------------|---|---|-------------|--------------|----------|----------|--------------|--------------|--------------|---|----|--------------|--------------|----|

|                                                        | (χ) <sup>τ</sup> 6    | <b>.</b>   | -            | 0 | 0 | 0           | -            | 0        | 0        | -            | -            | 0            | 1 | -  | 0            | -            | 0  |

|                                                        | (χ) <sup>ε</sup> δ    | 0          | -            | 0 | 0 | 0           | -            | -        | -        | 0            | -            | 0            | - | 0  | 0            | -            | 0  |

|                                                        | (x) <sup>†</sup> 6    | 0          | -            | - | - | <del></del> | -            | 0        | -        | <del></del>  | -            | 0            | 0 | -  | 0            | -            | -  |

|                                                        | (x) <sup>s</sup> 6    | 0          | 0            | 0 | - | 0           | -            | -        | 0        | 0            | 0            | -            | - | 0  | 0            | -            | 0  |

| Š                                                      | (x) <sup>9</sup> 6    | <b>—</b>   | 0            | 0 | - | 0           | -            | 0        | 0        | <del></del>  | 0            | 0            | - | 0  | 0            | 0            | -  |

| де БІ                                                  | (x) <sup>2</sup> 6    | <b>.</b> - | -            | 0 | - | <del></del> | -            | -        | 0        | 0            | -            | 0            | - | -  | 0            | -            | 0  |

| выхо                                                   | (χ) <sup>8</sup> δ    | 0          | <b>-</b>     | - | - | 0           | <b>—</b>     | -        | 0        | 0            | 0            | <b>—</b>     | 0 | 0  | <del>-</del> | 0            | 0  |

| а на                                                   | (X) <sup>1</sup> 4    | 0          | -            | 0 | - | 0           | _            | 0        | -        | -            | 0            | -            | 0 | -  | 0            | -            | 0  |

| ктор                                                   | (X) <sup>Z</sup> Y    | 0          | 0            | - | - | 0           | 0            | -        | -        | <del>-</del> | -            | 0            | 0 | -  | -            | 0            | 0  |

| ия ве                                                  | (X) <sup>E</sup> Y    | 0          | 0            | 0 | 0 | <b>—</b>    | _            | -        | -        | -            | _            | -            | - | 0  | 0            | 0            | 0  |

| элен                                                   | (X) <sup>†</sup> Y    | 0          | -            | 0 | 0 | -           | 0            | 0        | -        | <del>-</del> | 0            | 0            | - | 0  | 0            | -            | 0  |

| коррекцией способа доопределения вектора на выходе БКС | (X) <sup>S</sup> Y    | 0          | 0            | - | 0 | -           | 0            | 0        | 0        | 0            | 0            | 0            | - | 0  | -            | 0            | 0  |

| доог                                                   | (X) <sup>9</sup> 4    | 0          | 0            | 0 | 0 | <b>—</b>    | 0            | 0        | 0        | 0            | 0            | 0            | _ | 0  | 0            | 0            | 0  |

| soбa                                                   | (X) <sup>2</sup> 4    | 0          | 0            | 0 | - | 0           | 0            | _        | _        | <del>-</del> | <del>-</del> | 0            | 0 | -  | 0            | 0            | 0  |

| СПО                                                    | (X) <sup>8</sup> 4    | 0          | 0            | 0 | - | 0           | <del>-</del> | 0        | 0        | 0            | 0            | <del>-</del> | 0 | -  | 0            | 0            | 0  |

| цией                                                   | £ <sup>1</sup> (X)    | 0          | <b>—</b>     | - | 0 | 0           | <del>-</del> | _        | 0        | 0            | <del>-</del> | <del>-</del> | 0 | -  | 0            | 0            | -  |

| ррек                                                   | £ <sub>2</sub> (X)    | -          | <del></del>  | - | - | 0           | <del>-</del> | -        | -        | 0            | 0            | 0            | - | 0  | <del>-</del> | <del>-</del> | 0  |

| O                                                      | £3(X)                 | 0          | -            | 0 | 0 | <b>—</b>    | 0            | 0        | 0        | -            | 0            | -            | 0 | 0  | 0            | -            | 0  |

| CBK                                                    | ξ <sub>4</sub> (X)    | 0          | 0            | - | - | 0           | -            | 0        | 0        | 0            | -            | 0            | _ | -  | 0            | 0            | -  |

| твас                                                   | ξ <sup>2</sup> (χ)    | 0          | 0            | - | - | <b>—</b>    | -            | -        | 0        | 0            | 0            | -            | 0 | 0  | -            | -            | 0  |

| ройс                                                   | ξ <sup>e</sup> (χ)    | -          | 0            | 0 | - | <b>—</b>    | -            | 0        | 0        | -            | 0            | 0            | 0 | 0  | 0            | 0            | -  |

| уст                                                    | £ <sup>2</sup> (X)    | -          | -            | 0 | 0 | <b>—</b>    | -            | 0        | -        | -            | 0            | 0            | - | 0  | 0            | -            | 0  |

| аботь                                                  | f <sub>8</sub> (X)    | 0          | <del>-</del> | _ | 0 | 0           | 0            | <b>—</b> | 0        | 0            | 0            | 0            | 0 | _  | -            | 0            | 0  |

| иера                                                   | L <sub>X</sub>        | 0          | <del></del>  | 0 | _ | 0           | <del>-</del> | 0        | <b>—</b> | 0            | <del>-</del> | 0            | _ | 0  | -            | 0            | -  |

| Описание работы устройства с СВК                       | <sup>Z</sup> X        | 0          | 0            | _ | - | 0           | 0            | _        | -        | 0            | 0            | <b>—</b>     | _ | 0  | 0            | _            | -  |

|                                                        | ε <sub>χ</sub>        | 0          | 0            | 0 | 0 | _           | <del></del>  | _        | ~        | 0            | 0            | 0            | 0 | _  | <del></del>  | ~            | _  |

| ица 3                                                  | <sup>†</sup> х        | 0          | 0            | 0 | 0 | 0           | 0            | 0        | 0        | <del>-</del> | <del>-</del> | <del>-</del> | - | -  | <del>-</del> | _            | -  |

| Таблица 3.                                             | вдод <u>ь</u> н дэмоН | 0          | <b>—</b>     | 7 | m | 4           | 2            | 9        | 7        | <b>∞</b>     | 6            | 10           | 1 | 12 | 13           | 4            | 15 |

при числе выходов  $t \le 30$ , и чем это число меньше, тем, соответственно, быстрее будет находиться каждое решение задачи получения функций, описывающих выходы блока G(X) в CBK с учетом обозначенных выше ограничений.

# 6. О числе способов организации схем встроенного контроля

При синтезе СВК возникает задача выбора наилучшего способа ее реализации по заранее установленным показателям эффективности, например, по минимальным показателям структурной избыточности при обеспечении полной самопроверяемости структуры. Напомним, что при использовании традиционных подходов, основанных на дополнении информационных векторов контрольными векторами в СВК без какого-либо преобразования сигналов [2, 44, 45], имеется только один способ ее реализации для выбранного равномерного блокового кода с выбранной структурой тестера и способом реализации блока контрольной логики. При невозможности обеспечения полной самопроверяемости СВК или же при неудовлетворительных показателях ее структурной избыточности проектировщик высоконадежных и безопасных дискретных устройств вынужден прибегать к перебору иных кодов или стандартных методов (например, дублирования или контроля групп независимых выходов объекта диагностирования по паритету), либо же применять высоконадежную, использующую внутренние резервы компонентов, элементную базу. Покажем, что использование представленного в настоящей статье метода на практике дает серьезную вариативность выбора способа реализации СВК.

Число входов объекта диагностирования равно  $t \in \mathbb{N}$ . Число выходов определяется величиной  $(m+k) \in \mathbb{N}$ . Для контроля вычислений используется WS(m, k, M)-код. Число проверочных символов данного кода определяется величиной  $k = \lceil \log_2 M \rceil$ ,  $M \in \mathbb{N}$ ,  $M \ge 2$ . При этом далее рассматриваются только те модули, которые являются степенями двойки:

$$M \in \left\{2^{1}, 2^{2}, ..., 2^{\left\lceil \log_{2} W_{\max} \right\rceil - 1}, 2^{\left\lceil \log_{2} W_{\max} \right\rceil}\right\}, W_{\max} = 1 + \sum_{i=1}^{m} w_{i}.$$

Определим нижнюю и верхнюю оценки

количества способов организации СВК с применением WS(m, k, M)-кода для случая равномерного распределения информационных векторов между всеми контрольными (для неравномерного распределения количество способов синтеза СВК будет еще выше).

Так как при построении СВК требуется доопределение значений функций  $h_1(X)$ ,  $h_2(X)$ , ...,  $h_{m+k-1}(X)$ ,  $h_{m+k}(X)$  на каждом наборе значений аргументов и на наборах с десятичными эквивалентами  $(j, 2^t - 1 - j)$ ,  $j \in \{0, 1, ..., 2^{t-1} - 1\}$ , используются одинаковые кодовые слова WS(m, k, M)-кода, количество способов доопределения определяется количеством пар наборов значений аргументов. Оно равно  $2^{t-1}$ . На каждой такой паре существует возможность доопределения вектора  $< h_{m+k}(X) h_{m+k-1}(X) \dots h_2(X) h_1(X) >$  до одного из  $2^m$  кодовых слов WS(m, k, M)-кода. Отсюда получаем, что можно использовать

$$N_1 = \left(2^m\right)^{2^{\ell-1}} \tag{8}$$

вариантов доопределения.

Учитывая то, что при построении WS(m, k, M)-кода каждый разряд информационного вектора может быть взвешен натуральным числом из множества  $w_i \in \{1, 2, ..., M-1\}$ , отмечаем, что существует  $(M-1)^m$  способ построения WS(m, k, M)-кода [45]. Отсюда следует верхняя оценка количества способов организации СВК с контролем вычислений по двум диагностическим признакам по предложенному в настоящей статье методу:

$$\sup N = (M-1)^m (2^m)^{2^{t-1}}.$$

(9)

Выражение (9) — действительно именно верхняя оценка. Это становится ясным потому, что нельзя, например, доопределить все векторы  $< h_{m+k}(X) h_{m+k-1}(X) \dots h_2(X) h_1(X) >$  до одного и того же кодового слова WS(m, k, M)-кода, а формула (9) учитывает и эти варианты.

Если доопределять на каждой паре наборов значений аргументов векторы  $< h_{m+k}(X) \ h_{m+k-1}(X)...h_2(X) \ h_1(X) >$  до различных кодовых слов WS(m,k,M)-кода, то можно получить выражение для нижней оценки. Здесь возможны три случая: 1) t-1=m; 2) t-1 < m; 3) t-1 > m.

Первый случай t-1=m характеризует способ доопределения на каждом наборе значений аргументов  $2^{t-1}$  до одного из кодовых слов, соответствующих  $2^m$  неповторяющимся информационным векторам. Количество способов доопределения именно таким образом равно:

$$N_2 = 2^m (2^m - 1) \cdot \dots \cdot (2^m - (2^{t-1} - 1)) = (2^m)!. \quad (10)$$

Второй случай  $t-1 \le m$  указывает на то, что информационных векторов больше, чем наборов значений аргументов. Значит, количество способов доопределения в этом случае вычисляется по формуле:

$$N_2 = 2^m (2^m - 1) \cdot \dots \cdot (2^m - (2^{t-1} - 1)) = (2^m)^{\frac{2^{t-1} + 1}{2}}. (11)$$

В конечном выражении (11) присутствует убывающая факториальная степень

$$x^{p} = \frac{x!}{(x-p)!}$$

[58].

Наконец, третий случай t-1 > m связан с тем, что наборов значений аргументов больше, чем различных кодовых слов WS(m, k, M)-кода. Тогда для  $2^m$  наборов значений аргументов используем неповторяющиеся кодовые слова WS(m, k, M)-кода, а для оставшихся  $\left(2^{t-1} - 2^m\right)$  — любые. Итого, имеем следующее выражение для оценки числа способов доопределения:

$$N_2 = (2^m)!(2^m)^{2^{t-1}-2^m}. (12)$$

Учитывая количество способов построения WS(m, k, M)-кодов, получаем такие нижние оценки для всех трех случаев:

$$\inf N = \begin{cases} (M-1)^{m} (2^{m})!, t-1 = m, \\ (M-1)^{m} (2^{m})^{\frac{2^{t-1}+1}{2}}, t-1 < m, \\ (M-1)^{m} (2^{m})! (2^{m})^{2^{t-1}-2^{m}}, t-1 > m. \end{cases}$$

(13)

К примеру, для случая M = 4, m = 4 и t = 4 выражение (9) дает следующую оценку количества способов организации СВК:

$$\sup N = (4-1)^4 (2^4)^{2^{4-1}} = 3^4 \cdot 16^8 =$$

= 347 892 350 976.

Из выражения (13) получаем нижнюю оценку при тех же исходных данных:

$$\inf N = (4-1)^4 (2^4)^{\frac{2^{4-1}+1}{2}} = 3^4 \cdot (16)^{\frac{8}{2}} = 81 \cdot 16 \cdot 15 \cdot \dots \cdot 9 = 42 \cdot 032 \cdot 390 \cdot 400.$$

Разница между полученными числами составляет 305 859 960 576 (верхняя оценка дает в 8,277 раза большее число, чем нижняя).

Здесь полезным является получение выражения для оценки количества способов организации СВК по различным WS(m,k,M)-кодам с произвольными значениями k для одного и того же дискретного устройства с числом выходов n=m+k. Из (6) и того факта, что целесообразно использовать взвешенные коды с числом проверочных символов  $k \ge 2$ , следует:  $k \in \{2,3,...,t-1\}$ . Так как M является степенью двойки, то уместно записать  $M=2^k$ . Кроме того, заметим, что m=n-k. Используя приведенные здесь факты, получим верхнюю и нижнюю оценки числа способов построения СВК с использованием WS(m,k,M)-кодов по описанному в статье методу:

$$\sup N^* = \sum_{k=2}^{t-1} \left(2^k - 1\right)^{n-k} \left(2^{n-k}\right)^{2^{t-1}},\tag{14}$$

$\inf N^* =$

$$\begin{cases}

\sum_{k=2}^{t-1} (2^{k} - 1)^{n-k} (2^{n-k})!, t - 1 = n - k, \\

\sum_{k=2}^{t-1} (2^{k} - 1)^{n-k} (2^{n-k})^{\frac{2^{t-1} + 1}{2}}, t - 1 < n - k, \\

\sum_{k=2}^{t-1} (2^{k} - 1)^{n-k} (2^{n-k})! (2^{n-k})^{2^{t-1} - 2^{n-k}}, t - 1 > n - k.

\end{cases}$$

(15)

Третье выражение в формуле (15) при t-1 = n-k вырождается в первое. Если не использовать выражение для записи факториала, то все три формулы в (15) можно объединить в одну:

$$\inf N^* = \sum_{k=2}^{t-1} (2^k - 1)^{n-k} 2^{n-k} (2^{n-k} - 1) \cdot \dots \cdot (2^{n-k} - 2^{t-1} + 1) \Psi,$$

$$\Psi = \begin{cases} (2^{n-k})^{2^{t-1} - 2^{n-k}}, & t - 1 \ge n - k, \\ 1, & t - 1 < n - k. \end{cases}$$

(16)

К примеру, для случая n = 7 и t = 4 формулы (14) и (16) дают следующие оценки:

$$\sup N^* = \sum_{k=2}^{4-1} (2^k - 1)^{7-k} (2^{7-k})^{2^{4-1}} =$$

$$= (2^2 - 1)^{7-2} (2^{7-2})^{2^3} + (2^3 - 1)^{7-3} (2^{7-3})^{2^3} =$$

$$= 3^5 \cdot 32^8 + 7^4 \cdot 16^8 = 277 \cdot 493 \cdot 542 \cdot 027 \cdot 264,$$

$$\inf N^* = (2^2 - 1)^{7-2} (2^{7-2})^{\frac{2^{4-1}+1}{2}} + (2^3 - 1)^{7-3} (2^{7-3})! =$$

$$= 3^5 \cdot 32^9 + 7^4 \cdot 16! = 113 \cdot 367 \cdot 995 \cdot 485 \cdot 696.$$

Разница между полученными числами составляет 164 125 546 541 568 (верхняя оценка числа способов построения СВК дает в 2,448 раза большее число, чем нижняя). Данная разница обусловлена превышающим в 2,593 раза число способов доопределения при k=2, получаемых по формуле (14), в сравнении с числом, получаемым по формуле (15).

Число способов организации СВК по представленному в настоящей статье методу колоссально. При больших значениях t, m и M задача выбора наилучшего из всех вариантов становится трансвычислительной (причем достаточно быстро).

Показанные особенности говорят о том, что на практике, конечно, не следует перебирать все варианты синтеза СВК, а целесообразно ограничиться определенным количеством псевдослучайных вариантов, среди которых выбрать тот, который даст возможность формирования полных тестов для компонентов СВК и приемлемые показатели эффективности ее технической реализации.

# Заключение

Предложенный в настоящей статье метод организации СВК, основанный на ЛКС и применении WS(m, k, M)-кодов, позволяет синтезировать самопроверяемые дискретные устройства с улучшенными показателями контролепригодности в части наблюдаемости неисправностей на контрольных выходах по сравнению с традиционными методами. При этом следует отметить типизацию компонентов СВК и выделение стандартных модулей контроля вычислений по двум диагностическим

признакам, а также БКС. Основным вопросом, возникающим в ходе процедуры синтеза, является получение корректного описания логики функционирования блока G(X). Разработанный в ходе исследования алгоритм синтеза СВК позволяет это выполнить колоссальным количеством способов и дать разработчику высоконадежных дискретных устройств возможность выбора наилучшего решения по различным показателям эффективности.

Можно рассматривать применение структуры, приведенной на рис. 4, как при контроле всех выходов на основе одного WS(m, k, M)-кода, так и при выделении некоторого подмножества групп выходов с контролем вычислений на них отдельными подсхемами и с объединением их контрольных выходов на входах самопроверяемого компаратора (по аналогии с описанным, например, в [57]). Такой способ в ряде приложений может оказаться эффективным. Здесь также следует учесть и тот факт, что с ростом числа n у WS(m, k, M)-кодов расчет и число необнаруживаемых ими ошибок в кодовых словах. Целесообразно учитывать и особенности структуры объекта диагностирования при выборе способа выделения групп выходов, однако эта задача куда более сложна, чем может показаться, и требует отдельного исследования и отдельных публикаций по данному вопросу. Более того, при выделении групп выходов для контроля вычислений может оказаться более просто решаемой задача обеспечения самопроверяемости блоков в СВК.

При синтезе СВК для дискретных устройств по предложенному методу также могут эффективно использоваться схемы предварительного сжатия сигналов от объектов диагностирования, не приводящие к потере диагностической информации и к компенсации ошибок на выходах. Например, если структура объекта диагностирования такова, что она не допускает одновременных искажений значений на всех выходах, то целесообразно использовать схему сжатия n сигналов в n-1 сигнал без потери данных по методу из [59]. Это позволит упростить СВК. Могут быть использованы и иные схемы предварительного сжатия с учетом специфики структуры самого объекта диагностирования.

Использование структуры организации СВК по двум диагностическим признакам, предложенной в настоящей статье, эффективно при организации контроля вычислений в случае рассмотрения модели одиночных константных неисправностей (stuck-at модели мостиковой неисправности fault), (bridging fault) или модели транзистора (устойчивых обрывов транзисторов SOP (stuck-open) и устойчивых замыканий транзисторов SON (stuck-on)). Структура организации СВК может быть использована и на этапе проектирования дискретных устройств для выявления неисправностей вида «временная задержка» (delay fault), поскольку будет фиксировать искажения при формировании значений кодовых слов на параллельных выходах объекта диагностирования. Однако в каждом конкретном случае потребуется моделирование и анализ работы объекта диагностирования с СВК в условиях действия неисправностей из выбранной модели.

В качестве достоинства разработанного метода синтеза СВК можно выделить два ключевых аспекта. Первый — универсальность метода, заключающаяся в том, что абсолютно не важно, какой именно равномерный блоковый код будет использован при реализации алгоритма доопределения значений разрядов векторов  $< h_{m-k}(X) h_{m-k-1}(X) \dots h_2(X) h_1(X) >$ . При этом, однако, весьма интересным классом таких кодов, как показано в настоящей статье, является класс WS(m, k, M)-кодов. Второй плюс использования разработанного метода состоит в том, что он всегда дает возможность построения самопроверяемой структуры СВК, если это в принципе возможно с учетом особенностей объекта диагностирования (существуют примеры устройств, для которых не всегда это удается обеспечить). Недостатки же метода заключаются в необходимости анализа способов доопределения векторов  $< h_{m-k}(X) h_{m-k-1}(X) \dots h_2(X) h_1(X) >$ на каждом наборе значений аргументов, что приводит к большому количеству операций перебора информационных векторов. Однако алгоритм доопределения достаточно прост и может использоваться в режиме псевдослучайной генерации кодовых слов WS(m, k, M)-кодов на

первой половине таблицы описания работы объекта диагностирования с СВК. Сложности могут заключаться только в последующей после завершения процедуры доопределения значений разрядов векторов  $< h_{m-k}(X) \ h_{m-k-1}(X) \ ... \ h_2(X) \ h_1(X) >$  проверке тестируемости элементов XOR в БКС. Отдельной сложностью может оказаться использование метода с устройствами, работа которых задается на неполном множестве наборов значений аргументов.

Дальнейшие исследования могут быть сосредоточены в нескольких направлениях. Во-первых, интересен поиск такого алгоритма доопределения значений разрядов вектора  $\leq h_{m-k}(X)$   $h_{m-k-1}(X)$  ...  $h_2(X)$   $h_1(X) \geq$ , для которого автоматически будут учитываться и условия тестируемости элементов *XOR* в БКС. Во-вторых, не существует к настоящему времени и алгоритма взвешивания разрядов в информационных векторах при построении WS(m, k, M)-кодов на этапе их применения к конкретным объектам диагностирования, учитывающего возможности тестируемости элементов ХОР в БКС. В-третьих, пока что не установлены особенности использования разработанного метода при контроле вычислений по двум и более группам выходов с учетом свойств структур объектов диагностирования. В-четвертых, интересным направлением является анализ использования метода на различных тестовых примерах комбинационной и последовательностной логики, а также практическая реализация для устройств, синтезированных на современной программируемой элементной базе, и многие другие задачи.