УДК 681.518.5:004.052.32

### Д.В. Пивоваров

Кафедра «Автоматика и телемеханика на железных дорогах», Петербургский государственный университет путей сообщения Императора Александра I

# ОРГАНИЗАЦИЯ СИСТЕМ ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ СХЕМ НА ОСНОВЕ МЕТОДА ЛОГИЧЕСКОГО ДОПОЛНЕНИЯ ПО РАВНОВЕСНОМУ КОДУ «1 ИЗ 5»

При построении систем диагностирования логических устройств необходимо обеспечение полной самопроверяемости. В структурах функционального контроля, построенных по методу логического дополнения, данная проблема решается достаточно просто, так как один и тот же код может иметь различные реализации. Кроме того, выбирая способ реализации и последовательность выходов или способ разбиения выходов на группы, можно влиять как на сложность конечной структуры, так и на ее обнаруживающую способность.

При использовании метода логического дополнения имеет смысл использовать различные равновесные коды, так как в этом случае для полной самопроверяемости тестера достаточно обеспечить появление всех комбинаций равновесного кода. Ранее исследовались различные варианты построения схем по равновесным кодам «1 из 3» и «1 из 4». В данной статье анализируется один из вариантов построения схем на основе равновесного кода «1 из 5», а также влияние изменения последовательности выходов на сложность конечной структуры и ее обнаруживающую способность. Данный вариант дополнения до равновесного «1 из 5» кода был разработан так, чтобы в структурах, построенных по этому коду, обеспечивалась полная самопроверяемость как тестера, так и элементов «сложение по модулю два». Были проведены эксперименты на наборе контрольных примеров, имеющих 5 выходов. В ходе эксперимента анализировались характеристики структур со всеми возможными последовательностями выходов. Было показано, что последовательность выходов сильно влияет как на сложность конечной структуры, так и на ее обнаруживающую способность.

система диагностирования; логическое дополнение; равновесные коды; код «1 из 5»; функциональное диагностирование; площадь системы диагностирования

### Введение

В железнодорожной автоматике широко используются системы управления технологическими процессами на микропроцессорной и микроэлектронной основе. В подобных системах применяется функциональный контроль для обнаружения ошибок, возникающих в объектах диагностирования в ходе их работы. Системы функционального контроля должны обладать рядом возможностей, таких как обнаружение всех одиночных неисправностей, обес-

печение минимально возможной избыточности конечной структуры и самопроверяемости. Самопроверяемость подразумевает проявление любой неисправности заданного класса на выходах схемы хотя бы на одной из рабочих входных комбинаций. Наиболее часто рассматривается модель константных неисправностей — stuck-at faults [1]. Самопроверяемость обеспечивает защиту структуры от неисправностей возникающих во всех блоках системы функционального контроля. Для реализации этой возможности применяют методы синтеза самопроверяемых схем контроля [2–11]. В данной статье предложен способ построения системы функционального контроля по методу логического дополнения на основе равновесного кода «1 из 5».

### 1 Структурные схемы систем функционального контроля комбинационных схем

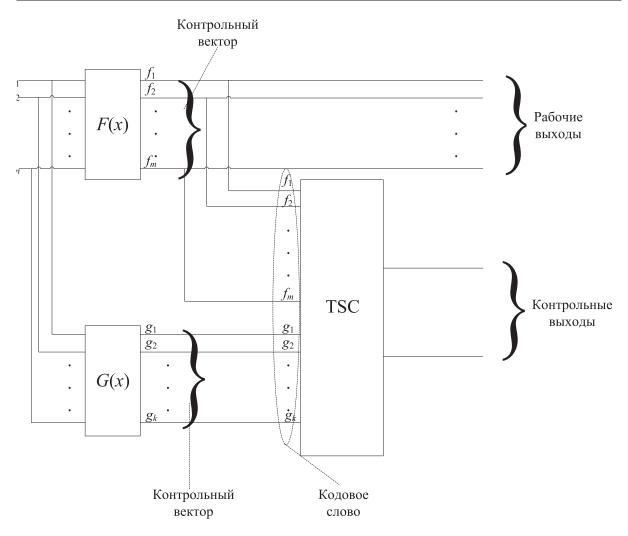

На рис. 1 изображена структурная схема системы диагностирования логического устройства F(x), реализующего ряд булевых функций  $f_1, f_2, ..., f_m$ . В целях контроля неисправностей объекта диагностирования по результатам вычислений функций он снабжен схемой контроля в составе блока контрольной логики G(x), вычисляющего ряд контрольных функций  $g_1, g_2, ..., g_k$ , и тестера TSC, сравнивающего значения функций  $f_1, f_2, ..., f_m$  и  $g_1, g_2, ..., g_k$  [12–14].

Система функционального контроля может быть построена разными способами. Одним из них является дублирование. В системе функционального контроля, построенной данным способом, блок G(x) полностью повторяет блок F(x), а тестер представляет собой компаратор, сравнивающий значения  $f_1, f_2, ..., f_m$  и  $g_1, g_2, ..., g_k$ . При несовпадении этих значений на выходе тестера появляется сигнал ошибки. Данный способ обеспечивает обнаружение всех одиночных неисправностей, однако сложность исходной схемы возрастает в 3–4 раза.

Гораздо менее сложен метод паритета. В системе функционального контроля, построенной данным способом, блок G(x) вычисляет бит четности, блок генератора тестера выполняет операцию «сложение по модулю два» всех выходов блока F(x), далее выходы блоков F(x) и G(x) сравниваются. У систем функционального контроля, построенных на основе данного способа, существует серьезный недостаток: они не обнаруживают все ошибки четной кратностью на выходах блока F(x).

Описанные выше способы относятся к методу вычисления контрольных разрядов. Согласно данному методу характеристики конечной структуры зависят от изначально выбранного кода. Для каждого кода существует только одна реализация структуры, что усложняет обеспечение полной самопроверяемости.

Рис. 1. Структурная схема системы диагностирования

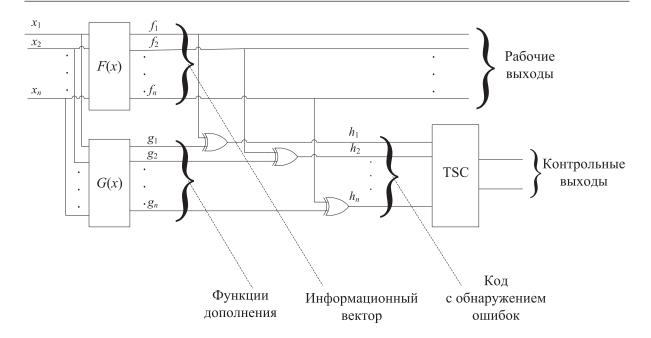

Кроме метода вычисления контрольных разрядов, существует метод логического дополнения. В системе функционального контроля, построенной по данному методу (рис. 2), блок контрольной логики G(x) вычисляет функции дополнения  $g_1, g_2, \ldots, g_n$ . Далее функции  $f_1, f_2, \ldots, f_n$  преобразуются в набор функций  $h_1, h_2, \ldots, h_n$  при помощи элементов «сложение по модулю два» и функций дополнения. Вектор  $h_1, h_2, \ldots, h_n$  должен принадлежать заранее выбранному равновесному коду.

Согласно данному методу системы диагностирования у одного кода может существовать множество реализаций и путем выбора этих реализаций можно обеспечить полную самопроверяемость структуры системы диагностирования и влиять на ее сложность и обнаруживающую способность [4, 15]. В структурах, построенных по методу вычисления контрольных разрядов, число разрядов контролируемого кода всегда больше, чем число информационных разрядов, а в системах функционального контроля, построенных по методу логического дополнения, число разрядов контролируемого кода

**Рис. 2.** Структурная схема системы функционального контроля, построенная по методу логического дополнения

равно числу информационных разрядов. Последнее существенно упрощает структуру тестера.

При реализации метода логического дополнения можно использовать различные равновесные коды. При их использовании для обеспечения самопроверяемости тестера достаточно, чтобы все слова равновесного кода появились на его входе хотя бы по одному разу. Хорошо исследованы вопросы применения равновесных кодов «1 из 3» [16–21], «1 из 4» [12, 13, 22–30] и «2 из 4» [31–34]. Рассмотрим особенности применения равновесного кода «1 из 5» при организации систем функционального контроля.

# 2 Особенности применения кода «1 из 5» при организации системы функционального контроля методом логического дополнения

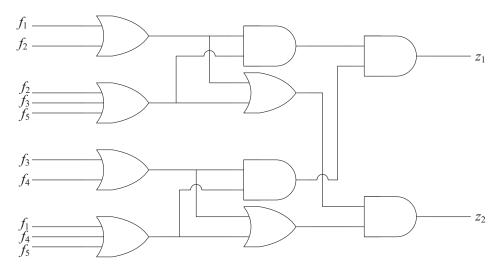

На рис. З изображена система функционального контроля, построенная по методу логического дополнения на основе равновесного кода «1 из 5». В данной структуре блок F(x) вычисляет пять разрядов информационного вектора, а блок G(x) — пять функций дополнения. Затем каждый информационный разряд складывается по модулю два с функцией дополнения и, таким образом, информационный вектор преобразуется в вектор кода «1 из 5».

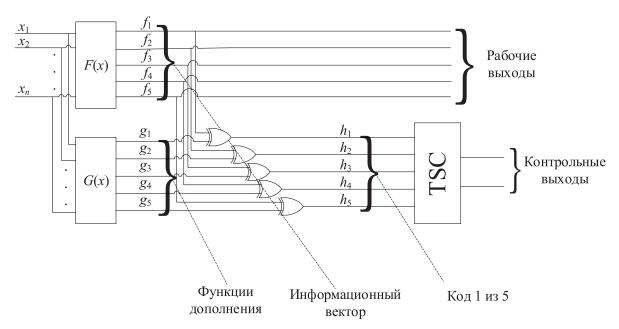

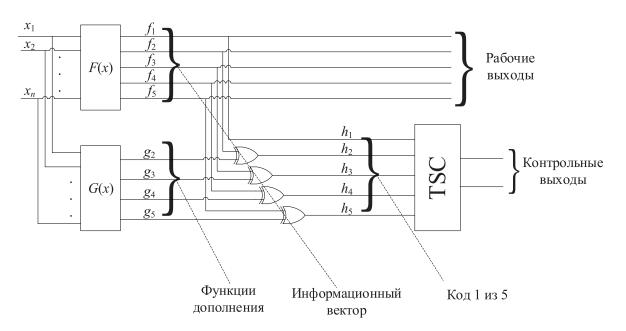

При использовании равновесного кода «1 из 5» нет необходимости вычислять все пять функций дополнения. Одну из них можно принять всегда

Рис. 3. Система функционального контроля, построенная по коду «1 из 5»

равной нулю. Тогда на соответствующий вход тестера можно подать соответствующий информационный разряд. Это несколько упрощает структуру (рис. 4).

В процессе работы системы диагностирования неисправности могут возникать не только в блоках F(x) и G(x), но и в тестере, и элементах «сложение по модулю два». Для обнаружения этих неисправностей необходимо, чтобы эти устройства обладали свойством самопроверяемости. Это свойство подраз-

**Рис. 4.** Система функционального контроля, построенная по коду «1 из 5» с четырьмя функциями дополнения

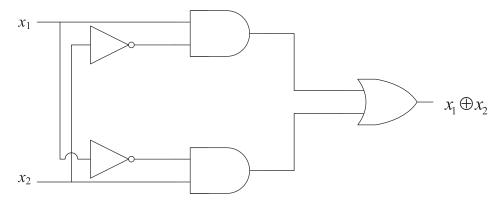

умевает, что при подаче на входы тестера некодового слова или при наличии внутреннего дефекта в тестере или элементе «сложение по модулю два» на выходах формируется сигнал ошибки. Самопроверяемость тестера (рис. 5) при использовании равновесного кода «1 из 5» достигается путем подачи всех слов кода на его входы во время нормальной работы устройства [35]. Самопроверяемость элементов «сложение по модулю два» (рис. 6) достигается путем поступления всех возможных комбинаций на входы этих элементов (00, 01, 10, 11) в процессе нормального функционирования устройства [36]. Таким образом, на входах тестера и элементов «сложение по модулю два» формируется полное множество тестовых комбинаций во время нормальной работы устройства.

Рис. 5. Структурная схема 1/5 TSC

Рис. 6. Структурная схема элемента «сложение по модулю два»

### 3 Способ вычисления функций дополнения по равновесному коду «1 из 5»

Как было сказано выше, необходимо разработать такой способ доопределения до кода «1 из 5», чтобы при его использовании на входе тестера по-

являлись все слова кода (00000, 00001, 00010, 00100, 01000, 10000) хотя бы по одному разу. Допустим, что не требуется доопределение функции  $f_5$ . Тогда на наборах  $< f_5 f_4 f_3 f_2 f_1 > = <1 \sim \sim \sim >$  должно формироваться только одно кодовое слово 1/5-кода -10000. На всех остальных 16 наборах  $< f_5 f_4 f_3 f_2 f_1 > = <0 \sim \sim \sim >$  должны сформироваться остальные кодовые слова 1/5-кода. При этом должно быть обеспеченно появление всего множества тестовых комбинаций на входы элементов «сложение по модулю два». Тестовые комбинации 00 и 11 появляются на наборах  $< f_5 f_4 f_3 f_2 f_1 > = <1 \sim \sim \sim >$ . На остальных наборах должны сформироваться комбинации 01 и 10.

Методом подбора были получены функции дополнения, обеспечивающие условия самопроверяемости (табл. 1). Правила вычисления формул логического дополнения нетрудно формализовать. Из таблицы непосредственно следуют выражения, описывающие функции логического дополнения:

$$\begin{cases} g_{1} = f_{4}f_{1} \vee f_{3}f_{1} \vee f_{2}f_{1} \vee f_{5}f_{1} \vee \overline{f_{5}} \ \overline{f_{4}}f_{3} \vee \overline{f_{5}}f_{3}\overline{f_{2}}; \\ g_{2} = f_{2}f_{1} \vee f_{5}f_{2} \vee f_{4}f_{2} \vee f_{3}f_{2} \vee \overline{f_{5}}f_{4}\overline{f_{3}} \ \overline{f_{2}} \vee \overline{f_{5}}f_{4}f_{3}f_{1} \vee \overline{f_{5}} \ \overline{f_{3}} \ \overline{f_{2}} \ \overline{f_{1}}; \\ g_{3} = \overline{f_{4}}f_{3}\overline{f_{1}} \vee f_{4}f_{3}f_{1} \vee f_{5}f_{3} \vee f_{3}\overline{f_{2}} \vee \overline{f_{5}} \ f_{4}\overline{f_{3}}f_{2}; \\ g_{4} = f_{4}\overline{f_{1}} \vee f_{5}f_{4} \vee f_{4}\overline{f_{3}}f_{2} \vee \overline{f_{5}}f_{3}\overline{f_{2}}f_{1} \vee \overline{f_{5}} \ \overline{f_{3}}f_{2}f_{1}. \end{cases}$$

$$(1)$$

Как видно из таблицы, каждая комбинация кода «1 из 5» появляется как минимум 4 раза. Это упрощает обеспечение свойства самопроверяемости, поскольку в реальных схемах на выходах не всегда появляются все возможные комбинации нулей и единиц. Из таблицы также видно, что на входах всех элементов «сложение по модулю два» все комбинации проверяющего теста появляются хотя бы по одному разу.

### 4 Результаты экспериментов

Для оценки характеристик систем функционального контроля, построенных при использовании описанного подхода были проведены эксперименты с набором контрольных примеров с пятью выходами MCNC Benchmark [37–39]. В табл. 2 приведены характеристики использованных в эксперименте схем.

В ходе эксперимента оценивались показатели структурной избыточности систем функционального контроля для выбранных тестовых комбинационных схем в объекте диагностирования. Для проведения подобных экспериментов было разработано специальное программное обеспечение, позволяющее по-

Таблица 1. Правила преобразования рабочих функций

| Десятичный эквивалент инфор- | Информационный<br>вектор | Функции<br>дополнения | Кодовое<br>слово 1/5-кода |  |  |

|------------------------------|--------------------------|-----------------------|---------------------------|--|--|

| мационного вектора           | $f_5 f_4 f_3 f_2 f_1$    | $g_5g_4g_3g_2g_1$     | $h_5 h_4 h_3 h_2 h_1$     |  |  |

| $n_{0}$                      | 00000                    | 00010                 | 00010                     |  |  |

| $n_1$                        | 00001                    | 00000                 | 00001                     |  |  |

| $n_2$                        | 00010                    | 00000                 | 00010                     |  |  |

| $n_3$                        | 00011                    | 01011                 | 01000                     |  |  |

| $n_4$                        | 00100                    | 00101                 | 00001                     |  |  |

| $n_{5}$                      | 00101                    | 01101                 | 01000                     |  |  |

| $n_{6}$                      | 00110                    | 00111                 | 00001                     |  |  |

| $n_7$                        | 00111                    | 00011                 | 00100                     |  |  |

| $n_8$                        | 01000                    | 01010                 | 00010                     |  |  |

| $n_9$                        | 01001                    | 00001                 | 01000                     |  |  |

| $n_{10}$                     | 01010                    | 01110                 | 00100                     |  |  |

| $n_{11}$                     | 01011                    | 01111                 | 00100                     |  |  |

| $n_{12}$                     | 01100                    | 01101                 | 00001                     |  |  |

| $n_{13}$                     | 01101                    | 01111                 | 00010                     |  |  |

| $n_{14}$                     | 01110                    | 01010                 | 00100                     |  |  |

| <i>n</i> <sub>15</sub>       | 01111                    | 00111                 | 01000                     |  |  |

| <i>n</i> <sub>16</sub>       | 10000                    | 00000                 | 10000                     |  |  |

| <i>n</i> <sub>17</sub>       | 10001                    | 00001                 | 10000                     |  |  |

| $n_{18}$                     | 10010                    | 00010                 | 10000                     |  |  |

| n <sub>19</sub>              | 10011                    | 00011                 | 10000                     |  |  |

| $n_{20}^{}$                  | 10100                    | 00100                 | 10000                     |  |  |

| $n_{21}$                     | 10101                    | 00101                 | 10000                     |  |  |

| $n_{22}$                     | 10110                    | 00110                 | 10000                     |  |  |

| $n_{23}$                     | 10111                    | 00111                 | 10000                     |  |  |

| $n_{24}^{}$                  | 11000                    | 01000                 | 10000                     |  |  |

| $n_{25}$                     | 11001                    | 01001                 | 10000                     |  |  |

| $n_{26}$                     | 11010                    | 01010                 | 10000                     |  |  |

| $n_{27}^{-}$                 | 11011                    | 01011                 | 10000                     |  |  |

| $n_{28}$                     | 11100                    | 01100                 | 10000                     |  |  |

| $n_{29}$                     | 11101                    | 01101                 | 10000                     |  |  |

| $n_{30}$                     | 11110                    | 01110                 | 10000                     |  |  |

| $n_{31}$                     | 11111                    | 01111                 | 10000                     |  |  |

| Название<br>схемы | Количество<br>входов | Количество<br>выходов | Площадь в условных единицах stdcell2_2.genlib |

|-------------------|----------------------|-----------------------|-----------------------------------------------|

| clpl              | 11                   | 5                     | 640                                           |

| dist              | 8                    | 5                     | 6968                                          |

| root              | 8                    | 5                     | 3496                                          |

Таблица 2. Характеристики выбранных контрольных комбинационных схем

лучить для заданных в формате \*.pla контрольных схем описание всех блоков системы функционального контроля в том же формате. После того как был получен файл-описание каждого блока, с помощью интерпретатора SIS и библиотеки функциональных элементов stdcell2\_2.genlib определялась площадь, занимаемая системой на кристалле, в условных единицах библиотеки. Далее описанный в данной статье способ сравнивался со способом, описанным в [40], в котором блок G(x) строится по следующим формулам:

$$\begin{cases} g_{1} = 0; \\ g_{2} = f_{1}f_{2}; \\ g_{3} = (f_{1} \vee f_{2})f_{3}; \\ g_{4} = (f_{1} \vee f_{2} \vee f_{3})f_{4}; \\ g_{5} = (f_{1} \vee f_{2} \vee f_{3} \vee f_{4})f_{5} \vee \overline{f_{1}} \overline{f_{2}} \overline{f_{3}} \overline{f_{4}} \overline{f_{5}}. \end{cases}$$

$$(2)$$

Таблица 3. Результаты экспериментов со схемами из набора MCNC Benchmarks

| На-<br>звание<br>схемы | Площади элементов системы диагностирования |      |                         | Площадь     | Площадь            | Площадь<br>системы<br>контроля | Показатели структурной избыточности, % |       |       |

|------------------------|--------------------------------------------|------|-------------------------|-------------|--------------------|--------------------------------|----------------------------------------|-------|-------|

|                        | F(x)                                       | G(x) | Блок<br>допол-<br>нения | 1/5-<br>TSC | диагности- рования | дублиро-<br>вания              | по формулам (2)                        | δ     | β     |

| clpl                   | 640                                        | 1661 | 160                     | 336         | 2301               | 2128                           | 2048                                   | 108   | 27,81 |

| dist                   | 6968                                       | 6246 | 160                     | 336         | 13214              | 14784                          | 11 920                                 | 89,38 | 52,73 |

| root                   | 3496                                       | 2399 | 160                     | 336         | 5895               | 7840                           | 5544                                   | 75,19 | 59,3  |

Результаты эксперимента занесены в табл. 3.

Как видно из таблицы, системы функционального контроля, построенные по предложенному автором методу, занимают большую площадь, чем системы, построенные на основе формул (2). Однако в системах функцио-

нального контроля, построенных на основе формул (2), не обеспечивается самопроверяемость всех элементов «сложение по модулю два».

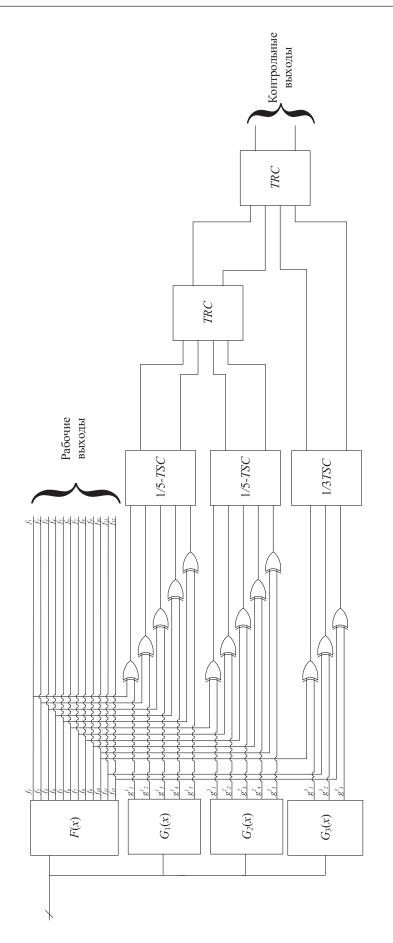

### 5 Контроль многовыходных схем на основе равновесного кода «1 из 5»

С помощью предложенного в данной статье метода можно строить системы функционального контроля и для схем с количеством выходов больше пяти. В подобном случае выходы исходной схемы делятся на группы и контроль происходит по группам выходов. При этом одни и те же выходы могут находиться в нескольких группах. Можно комбинировать также равновесный код «1 из 5» с другими равновесными кодами. На рис. 7 представлен пример построения системы функционального контроля по методу логического дополнения с использованием равновесных кодов «1 из 5» и «1 из 3» для контроля схемы с двенадцатью выходами. На данном примере выходы блока F(x) поделены на группы  $(f_1, f_2, f_3, f_4, f_5; f_6, f_7, f_8, f_9, f_1; f_{10}, f_{11}, f_{12})$ . На выходах блоков  $G_1(x)$  и  $G_2(x)$  формируются функции дополнения для кодов «1 из 5» для первых двух групп выходов. На выходах блока  $G_3(x)$  формируются функции дополнения для кода «1 из 3» для последней группы выходов. Далее кодовые векторы поступают на соответствующие тестеры равновесных кодов. Тестеры равновесных кодов объединяются при помощи модулей сжатия парафазных сигналов TRC.

#### Заключение

Предложенный в данной статье способ построения системы функционального контроля по методу логического дополнения на основе равновесного кода «1 из 5» позволяет в ряде случаев построить структуры, занимающие меньшую площадь, чем структуры дублирования, но большую, чем структуры на основе метода, описанного в [40]. Однако, в отличие от метода, описанного в [40], данный метод обеспечивает свойство самопроверяемости не только тестера, но и элементов «сложение по модулю два». Кроме того, предложенный способ позволяет равномерно формировать кодовые векторы кода «1 из 5», что важно и дает меньше входных слов для проверки. Был показан способ построения системы функционального контроля для схем с количеством выходов более 5. Перспективным направлением работы может быть более подробное исследование применения данного кода для контроля многовыходных схем.

Применение предложенного метода дополнения до кода «1 из 5» может быть использовано при реализации устройств автоматики на элементах программируемой логики типа FPGA.

Рис. 7. Построение системы функционального контроля по методу логического дополнения с использованием равновесных кодов «1 из 5» и «1 из 3» для контроля схемы с двенадцатью выходами

### Библиографический список

- 1. Matrosova A.Yu. Self-checking synchronous sequential circuit design for unidirectional error / A.Yu. Matrosova, S.A. Ostanin // Proceedings of the IEEE European test workshop (ETW'98), 27–29 May 1998, Sitges, Barcelona, Spain.

- 2. Согомонян Е.С. Самопроверяемые устройства и отказоустойчивые системы / Е.С. Согомонян, Е.В. Слабаков. – М.: Радио и связь, 1989. – 208 с.

- 3. Сапожников Вал. В. Самопроверяемые дискретные устройства / Вал. В. Сапожников, Вл. В. Сапожников. СПб. : Энергоатомиздат, 1992. 224 с.

- 4. Пархоменко П.П. Основы технической диагностики (оптимизация алгоритмов диагностирования, аппаратурные средства) / П.П. Пархоменко, Е.С. Согомонян. М.: Энергоатомиздат, 1981. 320 с.

- 5. Matrosova A. A Fault-tolerant sequential circuit design for SAFs and PDFs soft errors / A. Matrosova, S. Ostanin, I. Kirienko, E. Nikolaeva // 2016 IEEE 22nd International symposium on on-line testing and robust system design (IOLTS), 4–6 July 2016. Pp. 1–2.

- 6. Busaba F. Y. Self-checking combinational circuit design for single and unidirectional multibit errors / F. Y. Busaba, P. K. Lala // Journal of electronic testing: Theory and applications. 1994. Vol. 5. Issue 5. Pp. 19–28.

- 7. Das D. Synthesis of circuits with low-cost concurrent error detection based on bose-lin codes / D. Das, N.A. Touba // Journal of electronic testing: Theory and applications. 1999. Vol. 15. Issue 1–2. Pp. 145–155.

- 8. Das D. Low cost concurrent error detection based on modulo weight-based codes / D. Das, N. A. Touba, M. Seuring, M. Gossel // Proceedings of the 6th IEEE International on-line testing workshop (IOLTW), Spain, Palma de Mallorca, July 3–5, 2000. Pp. 171–176.

- 9. Nicolaidis M. On-line testing for VLSI A Compendium of approaches / M. Nicolaidis, Y. Zorian // Journal of electronic testing: Theory and application. 1998. Vol. 12. Issue 1–2. Pp. 7–20.

- 10. Mitra S. Which concurrent error detection scheme to choose? / S. Mitra, E. J. Mc-Cluskey // Proceedings of International test conference, 2000, USA, Atlantic City, NJ, 3–5 October 2000. Pp. 985–994.

- 11. Мехов В. Б. Контроль комбинационных схем на основе модифицированных кодов с суммированием / В. Б. Мехов, Вал. В. Сапожников, Вл. В. Сапожников // Автоматика и телемеханика. 2008. № 8. С. 153—165.

- 12. Пивоваров Д. В. Особенности организации полностью самопроверяемых структур на основе равновесного кода «1 из 4» / Д. В. Пивоваров // Материалы юбилейной XV Санкт-Петербургской Международной конференции «Региональная информатика 2016», Санкт-Петербург, 26—28 октября 2016 г. СПб. : СПОИСУ, 2016. С. 307—308.

- 13. Сапожников Вал. В. Метод логического дополнения на основе равновесного кода «1 из 4» для построения полностью самопроверяемых структур систем функционального контроля / Вал. В. Сапожников, Вл. В. Сапожников, Д. В. Ефанов, Д. В. Пивоваров // Электронное моделирование. 2017. Т. 39. № 2. С. 15—34.

- 14. Ефанов Д. В. О свойствах кода с суммированием в схемах функционального контроля / Д. В. Ефанов, Вал. В. Сапожников, Вл. В. Сапожников // Автоматика и телемеханика. 2010. № 6. С. 155—162.

- 15. Сапожников Вал. В. Самодвойственные дискретные устройства / Вал. В. Сапожников, Вл. В. Сапожников, М. Гессель. СПб. : Энергоатомиздат, Санкт-Петербургское отд-ние, 2001. 331 с.

- 16. Saposhnikov Val. V. Concurrent checking by Use of complementary circuits for «1-out-of-3» Codes / Val. V. Saposhnikov, A. Morozov, Vl. V. Saposhnikov, M. Goessel // 5th International workshop IEEE DDECS 2002, Brno, Czech Republic, April 17–19, 2002.

- 17. Гессель М. Логическое дополнение новый метод контроля комбинационных схем / М. Гессель, А. В. Морозов, Вал. В. Сапожников, Вл. В. Сапожников // Автоматика и телемеханика. 2003. № 1. С. 167–176.

- 18. Сапожников Вал. В. О синтезе полностью самопроверяемых комбинационных схем / Вал. В. Сапожников, Вл. В. Сапожников // Известия Петербургского университета путей сообщения. 2006. № 1. С. 97–110.

- 19. Das D. K. Constraint don't cares for optimizing designs for concurrent checking by 1-out-of-3 codes / D. K. Das, S. S. Roy, A. Dmitiriev, A. Morozov, M. Gössel // Proceedings of the 10th International workshops on boolean problems, Freiberg, Germany, September, 2012. Pp. 33–40.

- 20. Efanov D. Methods of organization of totally self-checking concurrent error detection system on the basis of constant-weight «1-out-of-3»-code / D. Efanov, Val. Sapozhnikov, Vl. Sapozhnikov // Proceedings of 14th IEEE East-West design & Test symposium (EWDTS'2016), Yerevan, Armenia, October 14–17, 2016. Pp. 117–125.

- 21. Сапожников Вал. В. Построение полностью самопроверяемых структур систем функционального контроля с использованием равновесного кода «1 из 3» / Вал. В. Сапожников, Вл. В. Сапожников, Д. В. Ефанов // Электронное моделирование. 2016. Т. 38. № 6. С. 25—43.

- 22. Сапожников Вал. В. Организация функционального контроля комбинационных схем методом логического дополнения / Вал. В. Сапожников, Вл. В. Сапожников, А. В. Дмитриев, А. В. Морозов, М. Гессель // Электронное моделирование. 2002. Т. 24. № 6. С. 51—66.

- 23. Сапожников Вал. В. Контроль комбинационных схем методом логического дополнения / Вал. В. Сапожников, Вл. В. Сапожников, Г. В. Осадчий // Конструирование, сертификация и техническая эксплуатация устройств и систем железнодорожной автоматики и телемеханики: сб. науч. тр. СПб.: Петербурсгкий гос. ун-т путей сообщения, 2003. С. 3—8.

- 24. Осадчий Г.В. Разработка метода логического дополнения для диагностирования и мониторинга устройств железнодорожной автоматики / Г.В. Осадчий // Известия Петербургского университета путей сообщения. 2004. № 1. С. 84–89.

- 25. Осадчий Г.В. Повышение эффективности использования метода логического дополнения для контроля комбинационных схем / Г.В. Осадчий // Разработка и эксплуатация новых устройств и систем железнодорожной автоматики и теле-

- механики : сб. науч. тр. СПб. : Петербурсгкий гос. ун-т путей сообщения, 2004. С. 32–35.

- 26. Saposhnikov Val. V. Design of totally self-checking combinational circuits by Use of complementary circuits / Val. V. Saposhnikov, Vl. V. Saposhnikov, A. Morozov, G. Osadtchi, M. Gossel // Proceedings of East-West design & Test workshop, Yalta, Ukraine, 2004. Pp. 83–87.

- 27. Гессель М. Контроль комбинационных схем методом логического дополнения / М. Гессель, А. В. Морозов, Вал. В. Сапожников, Вл. В. Сапожников // Автоматика и телемеханика. 2005. № 8. С. 161–172.

- 28. Göessel M. New methods of concurrent checking: Edition 1 / M. Göessel, V. Ocheretny, E. Sogomonyan, D. Marienfeld. Dordrecht: Springer science+business media B. V., 2008. 184 p.

- 29. Sen S. K. A Self-checking circuit for concurrent checking by 1-out-of-4 code with design optimization using constraint don't cares / S. K. Sen // National conference on emerging trends and advances in electrical engineering and renewable energy (NCEEERE'2010), Sikkim manipal institute of technology, Sikkim, held during, 22–24 December, 2010.

- 30. Пивоваров Д.В. Один способ построения полностью самопроверяемых структур систем функционального контроля на основе равновесного кода «1 из 4» / Д.В. Пивоваров // Информационные технологии на транспорте: сб. материалов секции «Информационные технологии на транспорте» юбилейной XV Санкт-Петербургской Международной конференции «Региональная информатика 2016», Санкт-Петербург, 26—28 октября 2016 г.; под. ред. Вал. В. Сапожникова. СПб.: ФГБОУ ВО ПГУПС, 2016. С. 17—27.

- 31. Ефанов Д. В. Применение равновесного кода «2 из 4» при организации систем функционального контроля / Д. В. Ефанов // Известия Петербургского университета путей сообщения. 2016. № 2. С. 269–278.

- 32. Сапожников Вал. В. Метод функционального контроля комбинационных логических устройств на основе кода «2 из 4» / Вал. В. Сапожников, Вл. В. Сапожников, Д. В. Ефанов // Известия вузов. Приборостроение. 2016. Т. 59. № 7. С. 524—533.

- 33. Sapozhnikov Val. Concurrent error detection of combinational circuits by the method of boolean complement on the base of «2-out-of-4» code / Val. Sapozhnikov, Vl. Sapozhnikov, D. Efanov // Proceedings of 14th IEEE East-West design & Test symposium (EWDTS'2016), Yerevan, Armenia, October 14–17, 2016. Pp. 126–133.

- 34. Сапожников Вал. В. Построение самопроверяемых структур систем функционального контроля на основе равновесного кода «2 из 4» / Вал. В. Сапожников, Вл. В. Сапожников, Д. В. Ефанов // Проблемы управления. 2017. № 1. С. 57—64.

- 35. Сапожников Вал. В. Организация систем функционального контроля с обеспечением полной самопроверяемости структуры на основе модулей сжатия парафазных сигналов / Вал. В. Сапожников, Вл. В. Сапожников, Д. В. Ефанов // Известия вузов. Приборостроение. 2017. Т. 60. № 5. С. 404–411.

- 36. Аксёнова Г. П. Необходимые и достаточные условия построения полностью проверяемых схем свертки по модулю два / Г. П. Аксёнова // Автоматика и телемеханика. 1979. № 9. С. 126—135.

- 37. Collection of digital design benchmarks. URL: http://ddd.fit.cvut.cz/prj/Benchmarks.

- 38. Yang S. Logic synthesis and optimization benchmarks: User Guide: Version 3.0 / S. Yang. Microelectronics center of Nth Carolina (MCNC), 1991. 88 p.

- 39. SIS: A system for sequential circuit synthesis / E.M. Sentovich, K.J. Singh, L. Lavagno, C. Moon, R. Murgai, A. Saldanha, H. Savoj, P.R. Stephan, R.K. Brayton, A. Sangiovanni-Vincentelli // Electronics research laboratory, Department of electrical engineering and computer science, University of California, Berkeley, 4 May 1992. 45 p.

- 40. Сапожников Вал. В. Способ построения системы функционального контроля на основе логического дополнения по равновесному коду «1 из 5» / Вал. В. Сапожников, Вл. В. Сапожников, Д. В. Ефанов, Д. В. Пивоваров // Радиоэлектроника и информатика. 2017. № 3. С. 28—35.

### Dmitry V. Pivovarov

«Automation and remote control on railways» department Emperor Alexander I St. Petersburg state transport university

## Organization of concurrent error-detection systems of combinational logical circuits on the basis of Boolean complement method with «1-out-of-5» constant-weight code

In the process of building diagnostics systems of logical units, the issue of providing full self-checking ability is particularly sensitive. In the structures of functional control, built by means of Boolean component method, the issue in question is solved fairly easily, as one and the same code may have different realizations. Also in the process of choosing the method of output realization and sequence, as well as the method of clustering outputs, one can influence both the finite structure's complexity and its detectivity.

In the process of Boolean complement method application it is convenient to use different constant-weight codes, as, in order to provide complete self-checking ability of a tester, it is sufficient to provide the appearance of all constant-weight code combinations, when using such codes. There are studies dealing with the investigation of different variants of building «1-out-of-3» and «1-out-of-4» constant-weight codes. One of the variants of building a «1-out-of-5» constant-weight code, as well as the influence of output sequence alteration on the finite structure's complexity and its detectivity, was analyzed in the given article. The introduced variant of a «1-out-of-5» constant-weight code was developed in such a way as to provide full self-checking ability of both the tester and «modulo two addition» elements in the structures built by this code. The experiments were conducted on

a number of benchmarks, having five outputs. Structures' characteristics with all possible output sequences were analyzed in the experiment. It was shown that the sequence of outputs markedly affects both the finite structure's complexity and its self-checking ability.

diagnostics system; Boolean complement; constant-weight codes; «1-out-of-5» code; on-line diagnostics system's area

#### References

- 1. Matrosova A.Yu., Ostanin S.A. (1998). Self-checking synchronous sequential circuit design for unidirectional error. Proceedings of the IEEE European test workshop (ETW'98), 27–29 May 1998, Sitges, Barcelona, Spain.

- 2. Sogomonyan E. S., Slabakov E. V. (1989). Self-checking devices and fault-tolerant ststems [Samoproveryaemye ustrojstva i otkazoustojchivye sistemy]. Moscow, Radio and communication [Radio i svyaz']. 208 p.

- 3. Sapozhnikov Val. V., Sapozhnikov Vl. V. (1992). Self-checking discrete devices [Samoproveryaemye diskretnye ustrojstva]. St. Petersburg, Energoatomizdat [Energoatomizdat]. 224 p.

- 4. Parhomenko P. P., Sogomonyan E. S. (1981). Basics of technical diagnostics (optimization of diagnostic algorithms and equipment) [Osnovy tekhnicheskoj diagnostiki (optimizaciya algoritmov diagnostirovaniya, apparaturnye sredstva)]. Moscow, Energoatomizdat [Energoatomizdat]. 320 p.

- 5. Matrosova A., Ostanin S., Kirienko I., Nikolaeva E. (2016). A Fault-tolerant sequential circuit design for SAFs and PDFs soft errors. 2016 IEEE 22nd International Symposium on on-line testing and robust system design (IOLTS), 4–6 July 2016. Pp. 1–2.

- 6. Busaba F. Y., Lala P. K. (1994). Self-checking combinational circuit design for single and unidirectional multibit errors. journal of electronic testing: Theory and applications, vol. 5, issue 5. Pp. 19–28.

- 7. Das D., Touba N.A. (1999). Synthesis of circuits with low-cost concurrent error detection based on bose-lin codes, Journal of electronic testing: Theory and applications, vol. 15, issue 1–2. Pp. 145–155.

- 8. Das D., Touba N.A., Seuring M., Gossel M. (2000). Low cost concurrent error detection based on modulo weight-based codes. Proceedings of the 6th IEEE International on-line testing workshop (IOLTW), Spain, Palma de Mallorca, July 3–5, 2000. Pp. 171–176.

- 9. Nicolaidis M., Zorian Y. (1998). On-line testing for VLSI A Compendium of approaches. Journal of electronic testing: Theory and application, vol. 12, issue 1–2. Pp. 7–20.

- 10. Mitra S., McCluskey E. J. (2000). Which concurrent error detection scheme to Choose? Proceedings of International test conference, USA, Atlantic City, NJ, 03–05 October 2000. Pp. 985–994.

- 11. Mekhov V.B., Sapozhnikov Val. V., Sapozhnikov Vl. V. (2008). Checking of combinational circuits basing on modification sum codes [Kontrol' kombinacionnyh skhem

- na osnove modificirovannyh kodov s summirovaniem]. Automation and Remote Control [Avtomatika i telemekhanika], issue 8. Pp. 153–165.

- 12. Pivovarov D. V. (2016). Features of the organization of totally self-checking structures on the basis of the «1-out-of-4» constant-weight code [Osobennosti organizacii polnost'yu samoproveryaemyh struktur na osnove ravnovesnogo koda «1 iz 4»]. Materials of the Jubilee XV St. Petersburg International conference «Regional informatics 2016», St. Petersburg, October 26–28, 2016 [Materialy Yubilejnoj XV Sankt-Peterburgskoj mezhdunarodnoj konferenciya «Regional'naya informatika 2016», Sankt-Peterburg, 26–28 oktyabrya 2016 g]. St. Petersburg, SPOISU [St. Petersburg, SPOISU]. Pp. 307–308.

- 13. Sapozhnikov Val. V., Sapozhnikov Vl. V., Efanov D. V., Pivovarov D. V. (2017). Boolean complement method based on constant-weight code «1-out-of-4» for formation of totally self-checking concurrent error detection systems [Metod logicheskogo dopolneniya na osnove ravnovesnogo koda «1 iz 4» dlya postroeniya polnost'yu samoproveryaemyh struktur sistem funkcional'nogo kontrolya]. Electronic modelling [Ehlektronnoe modelirovanie], vol. 39, issue 2. Pp. 15–34.

- 14. Efanov D. V., Sapozhnikov Val. V., Sapozhnikov Vl. V. (2010). On summation code properties in functional control circuits [O svojstvah koda s summirovaniem v skhemah funkcional'nogo kontrolya]. Automation and remote control [Avtomatika i telemekhanika], issue 6. Pp. 155–162.

- 15. Sapozhnikov Val. V., Sapozhnikov Vl. V., Goessel M. (2001). Self-dual discrete devices [Samodvojstvennye diskretnye ustroistva]. St. Petersburg, Energoatomizdat. 331 p.

- 16. Saposhnikov Val. V., Morozov A., Saposhnikov Vl. V., Goessel M. (2002). Concurrent checking by Use of complementary circuits for «1-out-of-3» Codes. 5th International workshop IEEE DDECS 2002, Brno, Czech Republic, April 17–19, 2002.

- 17. Gessel' M., Morozov A. V., Sapozhnikov Val. V., Sapozhnikov Vl. V. (2003). Logic complement, a new method of checking the combinational circuits [Logicheskoe dopolnenie novyj metod kontrolya kombinacionnyh skhem]. Automation and remote control [Avtomatika i telemekhanika], issue 1. Pp. 167–176.

- 18. Sapozhnikov Val. V., Sapozhnikov Vl. V. (2006). On totally self-checking combinational circuits synthesis [O sinteze polnost'yu samoproveryaemyh kombinacionnyh skhem]. Proceedings of Petersburg transport university [Izvestiya Peterburgskogo universiteta putej soobshcheniya], issue 1. Pp. 97–110.

- 19. Das D. K., Roy S. S., Dmitiriev A., Morozov A., Gössel M. (2012). Constraint don't cares for optimizing designs for concurrent checking by 1-out-of-3 Codes. Proceedings of the 10th International workshops on boolean problems, Freiberg, Germany, September, 2012. Pp. 33–40.

- 20. Efanov D., Sapozhnikov Val., Sapozhnikov Vl. (2016). Methods of organization of totally self-checking concurrent error detection system on the basis of constant-weight «1-out-of-3»-Code. Proceedings of 14th IEEE East-West design & Test symposium (EWDTS'2016), Yerevan, Armenia, October 14–17, 2016. Pp. 117–125.

- 21. Sapozhnikov Val. V., Sapozhnikov Vl. V., Efanov D. V. (2016). Formation of totally selfchecking structures of concurrent error detection systems with the Use of constant-weight Code «1-out-of-3» [Postroenie polnost'yu samoproveryaemyh struktur

- sistem funkcional'nogo kontrolya s ispol'zovaniem ravnovesnogo koda «1 iz 3»]. Electronic modelling [Ehlektronnoe modelirovanie], vol. 38, issue 6. Pp. 25–43.

- 22. Sapozhnikov Val. V., Sapozhnikov Vl. V., Dmitriev A. V., Morozov A. V., Gessel' M. (2002). Organization of functional checking of combinational circuits by the logic complement method [Organizaciya funkcional'nogo kontrolya kombinacionnyh skhem metodom logicheskogo dopolneniya]. Electronic modelling [Ehlektronnoe modelirovanie], vol. 24, issue 6. Pp. 51–66.

- 23. Sapozhnikov Val. V., Sapozhnikov Vl. V., Osadchij G. V. (2003). Combinational circuits checking by the method of boolean complement [Kontrol' kombinacionnyh skhem metodom logicheskogo dopolneniya]. Design, certification and technical operation of devices and systems of railway automation and remote control, Proceedings, St. Petersburg, PSTU [Konstruirovanie, sertifikaciya i tekhnicheskaya ehkspluataciya ustrojstv i sistem zheleznodorozhnoj avtomatiki i telemekhaniki, Sbornik nauchnyh trudov. Sankt-Peterburg, PGUPS]. Pp. 3–8.

- 24. Osadchij G. V. (2004). Development of a Boolean complement method for diagnosing and monitoring railway automation devices [Razrabotka metoda logicheskogo dopolneniya dlya diagnostirovaniya i monitoringa ustrojstv zheleznodorozhnoj avtomatiki]. Proceedings of Petersburg transport university [Izvestiya Peterburgskogo universiteta putej soobshcheniya], issue 1. Pp. 84–89.

- 25. Osadchij G.V. (2004). Increase the efficiency of the use of the method of logical addition for the control of combinational circuits [Povyshenie ehffektivnosti ispol'zovaniya metoda logicheskogo dopolneniya dlya kontrolya kombinacionnyh skhem]. Development and operation of new devices and systems of railway automation and remote control. Proceedings, St. Petersburg, PSTU [Razrabotka i expluataciya novyh ustrojstv i sistem zheleznodorozhnoj avtomatiki i telemekhaniki. Sbornik nauchnyh trudov. Sankt-Peterburg, PGUPS]. Pp. 32–35.

- 26. Saposhnikov Val. V., Saposhnikov Vl. V., Morozov A., Osadtchi G., Gossel M. (2004). Design of totally self-checking combinational circuits by Use of complementary Circuits. Proceedings of East-West design & Test workshop, Yalta, Ukraine, 2004. Pp. 83–87.

- 27. Gessel' M., Morozov A. V., Sapozhnikov Val. V., Sapozhnikov Vl. V. (2005). Checking Combinational circuits by the method of logic complement [Kontrol' kombinacionnyh skhem metodom logicheskogo dopolneniya]. Automation and remote control [Avtomatika i telemekhanika], issue 8. Pp. 161–172.

- 28. Göessel M., Ocheretny V., Sogomonyan E., Marienfeld D. (2008). New methods of concurrent checking. Edition 1. Dordrecht, springer science+business media B. V. 184 p.

- 29. Sen S. K. (2010). A Self-checking circuit for concurrent checking by 1-out-of-4 code with design optimization using constraint don't cares. National conference on emerging trends and advances in electrical engineering and renewable energy (NCEEERE'2010), Sikkim manipal institute of technology, Sikkim, held during 22–24 December, 2010.

- 30. Pivovarov D. V. (2016). One way of constructing completely self-checking structures of concurrent error-detection systems based on the «1-out-of-4» constant-weight code [Odin sposob postroeniya polnost'yu samoproveryaemyh struktur sistem

- funkcional'nogo kontrolya na osnove ravnovesnogo koda «1 iz 4»]. Information technologies at transport: proc. section «Information technologies at transport» of Anniversary XV St. Petersburg int. conf. «Regional informatics 2016», St. Petersburg, 26–28 of Oct. 2016; Ed. Val. V. Sapozhnikov [Informacionnye tekhnologii na transporte: sbornik materialov sekcii «Informacionnye tekhnologii na transporte» Yubilejnoj XV Sankt-Peterburgskoj mezhdunarodnoj konferencii «Regional'naya informatika 2016», Sankt-Peterburg, 26–28 oktyabrya 2016 g.; pod. red. Val. V. Sapozhnikova]. St. Petersburg, PSTU [PGUPS]. Pp. 17–27.

- 31. Efanov D. V. (2016). Application of the 2-Out-Of-4 Constant-weight code in organising concurrent error detection systems [Primenenie ravnovesnogo koda «2 iz 4» pri organizacii sistem funkcional'nogo kontrolya]. Proceedings of Petersburg transport university [Izvestiya Peterburgskogo universiteta putej soobshcheniya]. Issue 2.—Pp. 269–278.

- 32. Sapozhnikov Val. V., Sapozhnikov Vl. V., Efanov D. V. (2016). Method of operation control over combinatory logic device based on 2-Out-Of-4 Code [Metod funkcional'nogo kontrolya kombinacionnyh logicheskih ustrojstv na osnove koda «2 iz 4»]. Journal of instrument engineering [Izvestiya vuzov. Priborostroenie], vol. 59, issue 7. Pp. 524–533.

- 33. Sapozhnikov Val., Sapozhnikov Vl., Efanov D. Concurrent error detection of combinational circuits by the method of boolean complement on the base of «2-out-of-4» code. Proceedings of 14th IEEE East-West design & Test symposium (EWDTS'2016), Yerevan, Armenia, October 14–17, 2016. Pp. 126–133.

- 34. Sapozhnikov Val. V., Sapozhnikov Vl. V., Efanov D. V. (2017). Design of self-checking concurrent error detection systems based on «2-Out-Of-4» constant-weight code [Postroenie samoproveryaemyh struktur sistem funkcional'nogo kontrolya na osnove ravnovesnogo koda «2 iz 4»]. Problems of control [Problemy upravleniya], issue 1.— Pp. 57–64.

- 35. Sapozhnikov Val. V., Sapozhnikov Vl. V., Efanov D. V. (2017). Organization of functional control systems with totally self-checking structure based on paraphase signals compression modules [Organizaciya sistem funkcional'nogo kontrolya s obespecheniem polnoj samoproveryaemosti struktury na osnove modulej szhatiya parafaznyh signalov]. Journal of instrument engineering [Izvestiya vuzov. Priborostroenie], vol. 60, issue 5. Pp. 404–411.

- 36. Aksyonova G. P. (1979). Necessary and sufficient conditions for design of completely checkable modulo convolution circuits [Neobhodimye i dostatochnye usloviya postroeniya polnost'yu proveryaemyh skhem svertki po modulyu dva]. Automation and Remote Control [Avtomatika i telemekhanika], issue 9. Pp. 126–135.

- 37. Collection of digital design benchmarks. URL: http://ddd.fit.cvut.cz/prj/Benchmarks.

- 38. Yang S. (1991). Logic synthesis and optimization benchmarks: User guide: Version 3.0. Microelectronics center of Nth Carolina (MCNC). 88 p.

- 39. SIS: A System for sequential circuit synthesis / E.M. Sentovich, K.J. Singh, L. Lavagno, C. Moon, R. Murgai, A. Saldanha, H. Savoj, P.R. Stephan, R.K. Brayton, A. Sangiovanni-Vincentelli. Electronics research laboratory, Department of electrical engineering and computer science, University of California, Berkeley, 4 May 1992. 45 p.

40. Sapozhnikov Val. V., Sapozhnikov Vl. V., Efanov D. V., Pivovarov D. V. (2017). Way of formation of concurrent error detection system based on boolean complement with «1-out-of-5» code [Sposob postroeniya sistemy funkcional'nogo kontrolya na osnove logicheskogo dopolneniya po ravnovesnomu kodu «1 iz 5»]. Radioelectronics and Informatics [Radioehlektronika i informatika], issue 3. – Pp. 28–35.

Статья представлена к публикации членом редколлегии Д.В. Ефановым Поступила в редакцию 04.05.2017, принята к публикации 08.06.2017

Пивоваров Дмитрий Вячеславович — аспирант кафедры «Автоматика и телемеханика на железных дорогах» Петербургского государственного университета путей сообщения Императора Александра I. e-mail: pivovarov. d.v.spb@gmail.com

© Пивоваров Д. В., 2017